## Instructions on Placement and Routing by Encounter

- 1. Go to "run\_dir" folder, source /etc/software/edi Type "encounter" to start.

- 2. In the command window, type "set rda\_Input(ui\_pwrnet) {VDD}" and "set rda\_Input(ui\_gndnet) {VSS}". By using these 2 commands, we set two nets VDD and VSS.

- 3. Select File→Import RTL

In the "Logical" tab:

- Set "Verilog Files" to your synthesis result of Lab 4. It should be in "rc/syn/run\_dir" of your Lab 4 directory. *Please double-click the file to select*.

- For "Top Level", select "Auto Assign".

- Set "Max Libs" to the "tcbn65gpluswc.lib", which is located in "encounter/libdir/lib" folder.

- Set "Constraint Files" to the .sdc file which is generated in your Lab 4 and should be located in "rc/syn/run\_dir" directory of your Lab 4. It describes the constraint settings of your Lab 4. The RTL compiler outputted them as a file for Encounter to use.

In the "Physical" tab:

1. Set "LEF Files" to "tcbn65gplus\_8lmT2.lef", which is located in "encounter/libdir/lef". It contains the geometry information of the standard cells, which is needed during placement and routing.

Click "OK" to submit. Now, we finished specifying the inputs for placement and routing.

4. Select File $\rightarrow$ RTL Synthesis

Select "Proceed with Placement", and then click "OK". Ignore the warning about not specifying floorplan or def file.

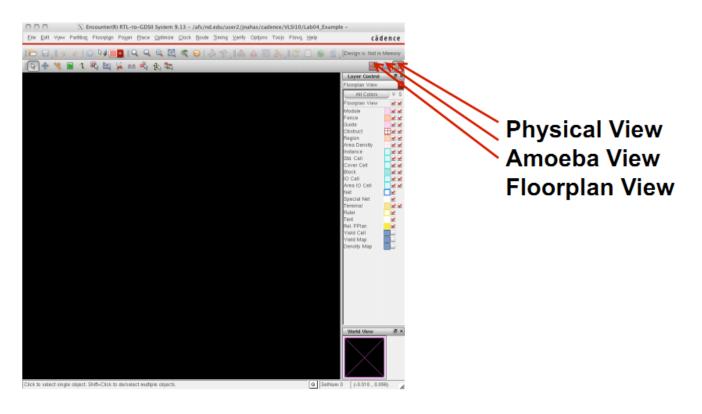

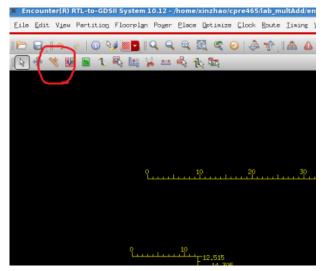

Now, please select the physical view to display your layout. You may need to press "F" to see the whole circuit.

| Eile Edit View Partition Floorplan Power Place Optimize Clock Route Iiming Verify Option | <sup>s PVS</sup> »cādence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ĨÊ ⊒ ]  > <   0 ₩ <b>∭⊒</b>    Q  Q  Q  Q  Q  (\$ \$ \$ ] &  Δ  Ⅲ  \$ \$                 | 🍇 i 🖀 🗒 🙆 😤                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                          | Image: Second |

|                                                                                          | M3(M3)<br>VIA3(V34)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                          | World View Ø×                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

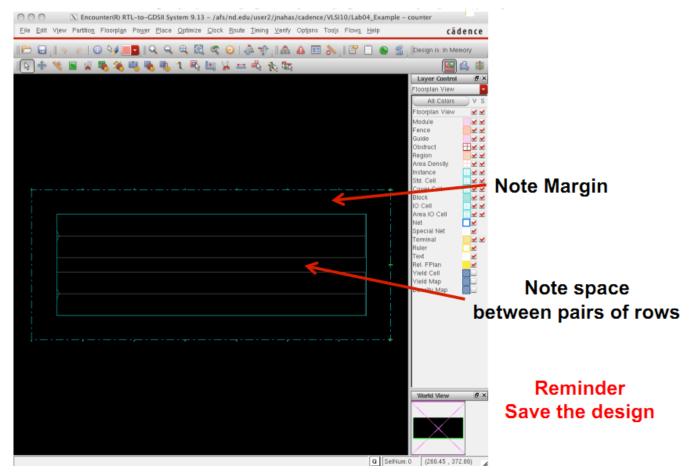

5. Select Floorplan→Specify Floorplan

Set the parameters and options for both "Basic" and "Advanced" tabs using the values as shown in the figures below. Please note that these parameters will affect your layout result.

| asic Advanced                       |                      |              |                 |

|-------------------------------------|----------------------|--------------|-----------------|

| Design Dimensions                   |                      |              |                 |

| Specify By: 💿 Size 🔾 Die/IO/Core Co | ordinates            |              |                 |

| 🥑 Core Size by: 💌 Aspect Ratio:     | Ratio (H/W):         | .6           | Aspect Ratio    |

|                                     | Core Utilization:    | 0.699881     |                 |

|                                     | Cell Utilization:    | 0.699881     | Can be adjusted |

| O Dimension:                        | Width:               | 252.9        | if desired      |

|                                     | Height:              | 108.0        | ii doon ou      |

| Die Size by:                        | Width:               | 314.1        |                 |

|                                     | Height:              | 168.0        | 30 micron       |

| Core Margins by: 🖲 Core to IO Boun  | dary                 |              |                 |

| Core to Die Bou                     | ndary                |              | margins add     |

| Core to Left:                       | 30 Core to Top:      | 30.0         | Left            |

| Core to Right:                      | 30.0 Core to Bottom: | 30.0         |                 |

| Die Size Calculation Use: O Max IO  |                      |              | Right           |

| Floorplan Origin at: 💿 Lower L      | eft Corner 🔾 Center  | Unit: Micron | Тор             |

|                                     |                      |              | Bottom          |

| OK Apply                            | <u>C</u> ancel       | Help         |                 |

Click Apply to see how floorplan changes affect layout on main screen

١

| 000                        | X Specify Floorplan    |      |                         |

|----------------------------|------------------------|------|-------------------------|

| Basic Advanced             |                        |      |                         |

| Standard Cell Rows         |                        |      |                         |

| Double-back Rows:          | Bottom Row Orient: 🗾 🕨 |      |                         |

| Row Spacing: 18            | e Ear Every 2 Now      |      |                         |

| Site: core Row Height:     |                        |      | 18 micron spacing added |

| Allow Overlapping Same     | Site Rows              |      |                         |

| 10 Specifications          |                        |      |                         |

| Bottom IO Pad Orientation: |                        |      |                         |

| Use I/O Rows for I/O Place | ement                  |      |                         |

|                            |                        |      |                         |

|                            |                        |      |                         |

|                            |                        |      |                         |

|                            |                        |      |                         |

|                            |                        |      |                         |

|                            |                        |      |                         |

|                            |                        |      | Click OK when done      |

|                            |                        |      |                         |

| <u>o</u> k ←               | Apply <u>C</u> ancel   | Help | 4                       |

Then the placement region will be displayed:

### 6. Select Power → Power Planning → Add Ring

Set the parameters and options for "Basic" tab using the values as shown in the figure below.

| VDD VSS                 |

|-------------------------|

| VDD VSS                 |

| VDD VSS                 |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

| Ding widths to 0.0      |

| Ring widths to 9.9      |

| _                       |

| ——— Ring spacing to 1.3 |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

| Click OK                |

|                         |

|                         |

|                         |

|                         |

|                         |

|                         |

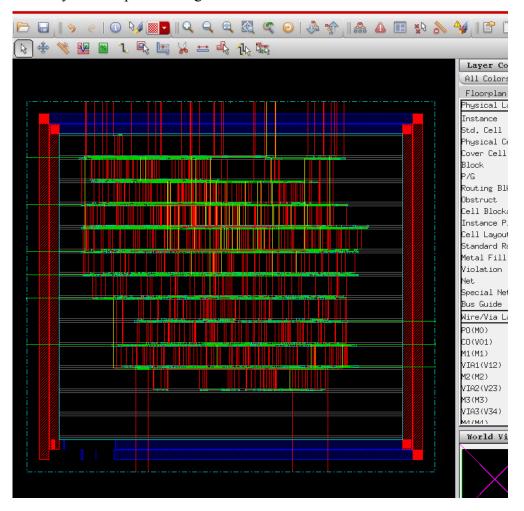

Then the power rings will be displayed:

| 🏱 🖬 🛯 🦻 🖉 🚺 🗣 🔍 역 🚳 🍳 👘 🕼 🕼 🖬 🕼 🕬       | » 🔍 ۱۳ 🕻 🤞               |

|-----------------------------------------|--------------------------|

| 💫 🚸 💘 📟 1. 🖳 📖 🦗 🖴 🔩 🦍 🐯                |                          |

|                                         | Layer Co                 |

|                                         | (All Colors)             |

|                                         | Floorplan Ph             |

| · ····································  | Physical Layers          |

|                                         | Instance                 |

|                                         | Std. Cell                |

|                                         | Physical Cell            |

|                                         | Cover Cell               |

|                                         | Block                    |

|                                         | P/G                      |

|                                         | Routing Blkg<br>Obstruct |

|                                         | Cell Blockage            |

|                                         | Instance Pin             |

|                                         | Cell Layout              |

|                                         | Standard Row             |

| l i li | Metal Fill               |

|                                         | Violation                |

|                                         | Net [                    |

|                                         | Special Net              |

|                                         | Bus Guide [              |

|                                         | Wire/Via Layers          |

|                                         | PO(MO)                   |

|                                         | CD(V01)<br>M1(M1)        |

| i i                                     | VIA1(V12)                |

|                                         | M2(M2)                   |

|                                         | VIA2(V23)                |

|                                         | M3(M3)                   |

|                                         | VIA3(V34)                |

|                                         | малмал 🔽                 |

|                                         | World View               |

|                                         |                          |

|                                         |                          |

|                                         |                          |

|                                         |                          |

### 7. Select Place $\rightarrow$ Place Standard Cell

Set the options as shown in the figure below.

| 000                                    | X Place                                                         |

|----------------------------------------|-----------------------------------------------------------------|

| 🖲 Run Full Placeme                     | t 🔾 Run Incremental Placement 🔾 Run Placement In Floorplan Mode |

| - Optimization Option                  |                                                                 |

| ✓ Include Pre-Place ☐ Include In-Place |                                                                 |

| Number of Local CPU(                   | ): 1 Set Multiple CPU                                           |

|                                        | pply <u>M</u> ode <u>D</u> efaults <u>C</u> ancel <u>H</u> elp  |

|                                        |                                                                 |

|                                        |                                                                 |

| Le                                     | ave Defaults – just click OK                                    |

You may need to press "F" again to view the whole circuit.

8. Select Optimize → Optimize Design

Set the options as shown in the figure below.

| 000               | 🔀 Optimizat               | ion                              |                                                 |

|-------------------|---------------------------|----------------------------------|-------------------------------------------------|

| Design Stage      |                           |                                  |                                                 |

| Pre-CTS           | Post-CTS                  | O Post-Route                     |                                                 |

| Optimization Type | 9                         | Pre-CTS                          | <ul> <li>Before Clock Tree Synthesis</li> </ul> |

| 🗹 Setup           | Ш н                       | old                              |                                                 |

| Incremental       |                           |                                  |                                                 |

| 🖲 Design Rules V  | iolations                 |                                  |                                                 |

| 🛃 Max Cap         |                           |                                  |                                                 |

| 🗹 Max Tran        |                           |                                  |                                                 |

| 🔲 Max Fanout      |                           |                                  |                                                 |

| 🗌 Include SI 💽    | Options)                  |                                  | <ul> <li>Click OK</li> </ul>                    |

|                   | y <u>M</u> ode <u>D</u> e | fault <u>C</u> lose <u>H</u> elp |                                                 |

# Note: You might get an error message Ignore for now.

"CTS" means clock tree synthesis. Pre-CTS means before clock tree synthesis. In here, please note that we have selected the option to correct setup time violations.

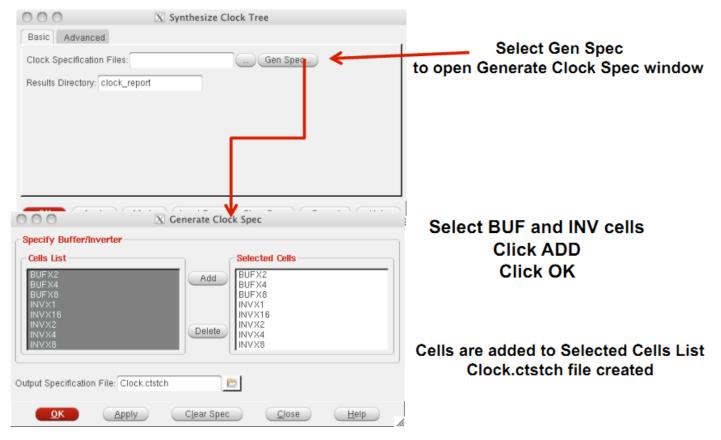

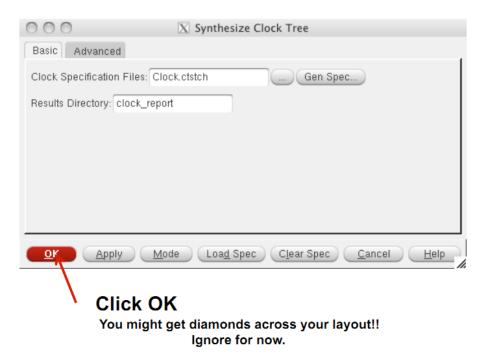

9. Select Clock  $\rightarrow$  Synthesize Clock Tree

Set the options as shown in the figures below.

You can view the clock tree by selecting Clock $\rightarrow$ Display $\rightarrow$ Display Clock Tree.

10. Select Optimize → Optimize Design again Set the options as shown in the figure below.

| 000                      | 🔀 Optimizati             | on                      |

|--------------------------|--------------------------|-------------------------|

| Design Stage             |                          |                         |

| O Pre-CTS                | Post-CTS                 | Post-Route              |

| Optimization Type        |                          |                         |

| ⊻ Setup                  | 📃 Ho                     | old                     |

| Incremental              |                          |                         |

| 🖲 Design Rules Viola     | tions                    |                         |

| 🗹 Max Cap                |                          |                         |

| 🗹 Max Tran               |                          |                         |

| 📃 Max Fanout             |                          |                         |

| 🗌 Include SI 🛛 SI Op     | tions)                   |                         |

| <u>O</u> K <u>A</u> pply | <u>M</u> ode <u>D</u> ef | ault <u>Close H</u> elp |

We selected Post-CTS this time. It means the optimization is performed after clock tree synthesis.

### 11. Select Route→NanoRoute→Route

Set the parameters and options as shown in the figure below.

| 000                 | X NanoRoute                                 |

|---------------------|---------------------------------------------|

| Routing Phase       |                                             |

| 🗹 Global Route      |                                             |

| ⊻ Detail Route      | Start Iteration 0 End Iteration default     |

| Post Route Optimi   | zation 📃 Optimize Via 📃 Optimize Wire       |

| Concurrent Rout     | ing Features                                |

| 🗹 Fix Antenna       | 🔄 Insert Diodes 🛛 Diode Cell Name           |

| Timing Driven       | Effort 5 Congestion Timing S.M.A.R.T.       |

| SI Driven           |                                             |

| Post Route SI       | SI Victim File 📄                            |

| 🔲 Litho Driven      |                                             |

| 🔲 Post Route Lith   | io Repair                                   |

| - Routing Control - |                                             |

| Selected Nets       | Only Bottom Layer default Top Layer default |

| ECO Route           |                                             |

| 🔲 Area Route        | Area Select Area and Route                  |

| Job Control         |                                             |

| 🛃 Auto Stop         |                                             |

| Nu                  | imber of Local CPU(s): 1                    |

| Number of CUP(s)    | per Remote Machine: 1                       |

| Number              | of Remote Machine(s): 0                     |

| Set Multiple C      | PU                                          |

|                     | ny Attribute Mode Save Load Cancel Help     |

### 12. Select Optimize → Optimize Design

This time, we select Post-Route because we have already performed routing.

- 13. Now you have finished placement and routing.

- To report power, type report\_power.

- To get area information, use the ruler which is circled by red below:

- To report worst timing path, type report\_timing in the command window.

- To debug timing violations, select Timing→Debug Timing.

- To save your design, type "saveNetlist -excludeLeafCell design\_pr.v" in the command window.

- To output RC parameters of your design, type "rcOut -spef design.spef" in the command window.

- To output .sdf (Standard Delay Format) file, select Timing→Write SDF. The .sdf file contains the information required for signal delay calculation. This file would be needed if we perform post layout simulation in ModelSim.