# Triangle Rendering Engine

EE 465 Final Project

10 December 2015

Cory Snooks Aaron Pedersen

# Contents

| Introduction                                     |

|--------------------------------------------------|

| Design Methodology                               |

| Point is to the right or left of a slanted line4 |

| Throughput5                                      |

| Case 1 - Left-facing triangle:                   |

| Case 2 - Right-facing triangle:5                 |

| Device Sharing6                                  |

| Verilog Code7                                    |

| RTL Synthesis14                                  |

| Layout15                                         |

| Results15                                        |

| Conclusion                                       |

| Appendix                                         |

| ModelSim                                         |

| RTL Synthesis Instructions                       |

| Encounter Instructions22                         |

| run_synth.tcl                                    |

| design.sdc32                                     |

| triangle_tb.v                                    |

# Introduction

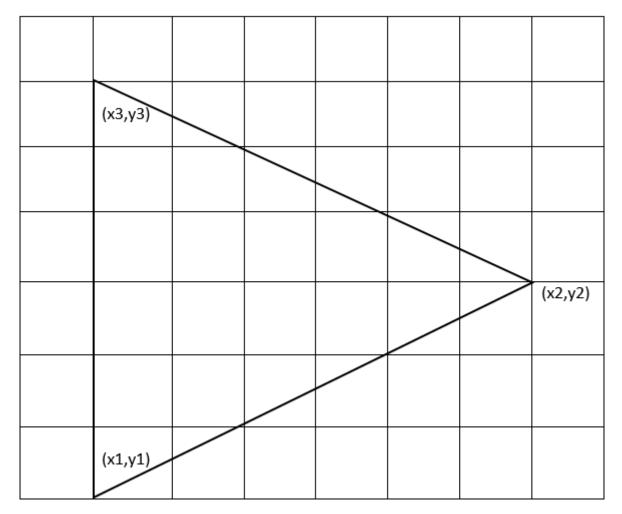

This project consisted of writing the Verilog code, performing RTL synthesized, and completing layout for a triangle rendering engine (TRE). The TRE took three sets of 3-bit x, y coordinate inputs and returned all of the points contained within the triangle. The TRE had to be functional for the base cases of x1 = x3 and y1 < y2 < y3. The input triangles could be left or right facing and were limited to a minimum coordinate value of zero and a maximum coordinate value of seven. A test bench was provided for the project that checked all of the outputs for the both facing triangles. The Verilog code was synthesized after the functionality was deemed correct to ensure that the code was physically possible. After solving some multiple driver errors, a full layout of the circuit was completed.

Figure 1: A sample triangle is shown above.

# Design Methodology

From the hint given in the project specifications, the equation to determine if a point on a line is as follows:

$$\frac{x - x_1}{y - y_1} - \frac{x_2 - x_1}{y_2 - y_1} = 0$$

If the point is to the right hand side of the line, this equation is true:

$$\frac{x - x_1}{y - y_1} - \frac{x_2 - x_1}{y_2 - y_1} > 0$$

If the point is to the left hand side of the line, this equation is true:

$$\frac{x - x_1}{y - y_1} - \frac{x_2 - x_1}{y_2 - y_1} < 0$$

For our design we will use a modification of these equations in order to accurately determine if a coordinate was located in the triangle. The direction of the triangle had to be found by comparing the value of x1 to x2 in order to determine which metric to compare the equation to. If x1 < x2 then the triangle is right facing and if x1 > x2 then the triangle is left facing.

To compute whether a point of interest is inside the triangle, we will be using the following assumptions:

- $y_1 = y_3$

- $y_1 1 < y_2 < y_3$

Manipulating the equation  $\frac{x-x_1}{y-y_1} - \frac{x_2-x_1}{y_2-y_1} = 0$ , we can derive the equation:  $\frac{x-x_1}{y-y_1} = \frac{x_2-x_1}{y_2-y_1} \rightarrow (x-x_1)(y_2-y_1) - (x_2-x_1)(y-y_1)$

To do all these computations in one clock cycle, we would need 2 multipliers and 5 adders. To implement sharing of these blocks, we will do these computations in multiple clock cycles. For our design, we used the following variables to represent parts of the equation:

$$(x - x_1) \text{ or } (x - x_3) = A$$

$$(y - y_1) \text{ or } (y - y_3) = B$$

$$(x_2 - x_1) = C0$$

$$(y_2 - y_1) = D0$$

$$(x_2 - x_3) = C1$$

$$(y_2 - y_3) = D1$$

$$(x - x_1)(y_2 - y_1) = AD$$

$$(x_2 - x_1)(y - y_1) = BC$$

$$(x - x_1)(y_2 - y_1) - (x_2 - x_1)(y - y_1) = RL0$$

To generate the desired output, we must start by analyzing the (x1, y1) coordinate and outputting that. Then we must increment an x variable to analyze new (x,y) coordinates. When the row is finished outputting all valid points, we must then increment y and repeat the process until all points are checked.

Since y does not change when scanning one row, we will only need to compute B once for each row. We have implemented this in the code.

## Point is to the right or left of a slanted line

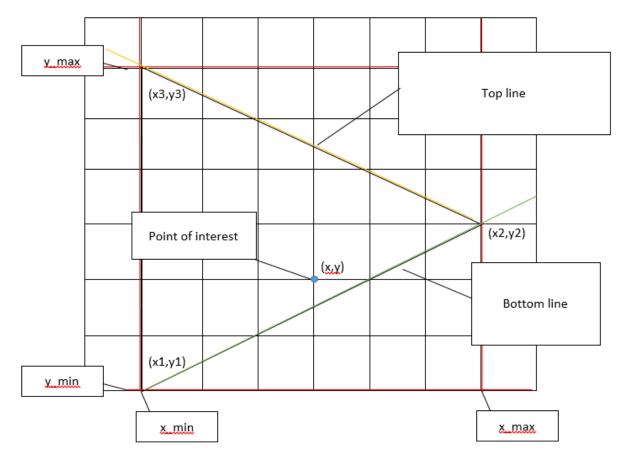

First, we need to know if the line we want to compare a coordinate to is the upper line of the triangle or the lower line of the triangle. To do this, we simply compare the y value of the coordinate of interest to the y2 value that was input. If the y value of interest is greater than the y2 value, then the line we want to compare to is the upper line. If it is equal to y2, we still compare it to the bottom line.

When comparing the current coordinates against the bottom line, x-x1 was stored into register A, y-y1 was stored into register B, x2-x1 was stored into register C0 and y2-y1 was stored into register D0. When comparing the current coordinates against the top line, x-x3 was stored into register A, y-y3 was stored into register B, x2-x3 was stored into register C1 and y2-y3 was stored into register D1. With these three things known (if it is an upper line, if the triangle is right facing or left facing, and the RLO result), we can tell if the point is valid or not.

For bottom lines, if RLO is positive, the point is right of the line. For top lines, if RLO is negative, the point is to the right of the line. If RLO is zero, the point is on the line.

Figure 2: The diagram above shows how the Verilog broke down an input triangle and found coordinates inside of the triangle.

#### Throughput

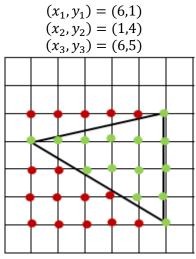

The throughput for this design methodology is quite complicated to report. For every new row, B and BC values are calculated only once and there are different sizes/layouts of right and left-facing triangles. For right facing triangles there is one extra point analyzed which is not in the triangle boundary, whereas for left facing triangles all points inside a rectangle must be analyzed. The rectangle coordinates are (x2, y1), (x2, y3), (x1, y1), (x3, y3).

#### Case 1 - Left-facing triangle:

In this case, we waste clock cycles because we must start at x\_min. We could generate an algorithm that calculates the first valid x coordinate, but that would be time consuming and make the design more complicated and area-consuming.

Figure 3: Example Left-facing Triangle

$$(x_1 - x_2 + 1) \times (y_3 - y_1 + 1) \times 5 + (y_3 - y_1 + 1) \times 2 + 4$$

#### Case 2 - Right-facing triangle:

In this case, we can detect a "negative edge" of valid outputs and decide to move on to the next row in order to save some clock cycles.

Figure 4: Example Right-facing Triangle

(# of points in the triangle)  $\times 5 + (y_3 - y_1 + 1) \times 2 + (y_3 - y_1) \times 5 + 4$

## Device Sharing

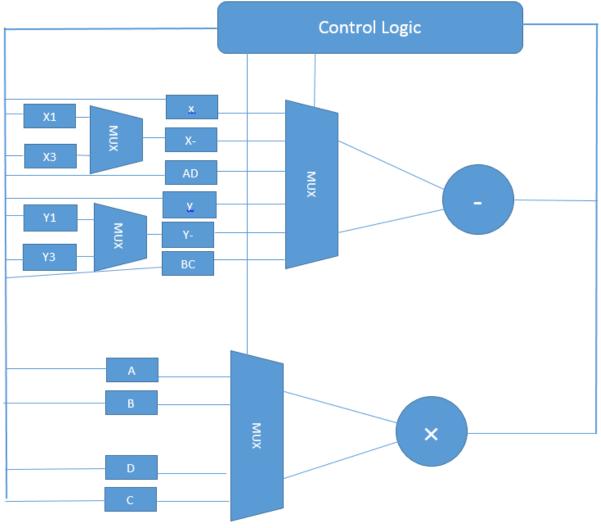

Here is a top-level concept diagram of the sharing functionality of the design:

Figure 5: Device sharing block diagram

The thicker line is a bus which selects signals from the outputs of the multiplier or adder depending on which state the system is in. This is a rough diagram to show the basic idea of sharing the multiplier and adder.

#### Verilog Code

`timescale 100ps/10ps module triangle(clk, reset, nt, xi, yi, busy, po, xo, yo); input clk, reset, nt; **input** [2:0] xi, yi; output busy, po; output [2:0] xo, yo; wire clk, reset, nt; wire [2:0] xi, yi; reg [2:0] xo, yo, x min, x max, y min, y max, x, y; reg [2:0] xi ff[2:0], yi ff[2:0]; reg busy, good, mul en, sub en, check, rst int, inc y, inc x; //internal reset reg po, po , on line, right line , right triangle, top line; //right triangle = 1 means right, 0 means left reg signed [6:0] sub\_ans , sub\_op0, sub\_op1, mul\_op0, mul\_op1; reg signed [6:0] mul ans, A, B, C0, D0, C1, D1, AD, BC, RLO; reg [3:0] control, control 1;

```

always @ (posedge clk)begin

if(reset || rst_int) begin

xi ff[0] <= 0;</pre>

xi ff[1] <= 0;</pre>

xi ff[2] <= 0;</pre>

yi ff[0] <= 0;</pre>

yi ff[1] <= 0;</pre>

yi ff[2] <= 0;</pre>

x min <= 7;

x max <= 0;</pre>

y min <= 7;

y max <= 0;

top line <= 0;</pre>

A <= 0;

B <= 0;

CO <= 0;

C1 <= 0;

D0 <= 0;

D1 <= 0;

AD <= 0;

BC <= 0;

RLO <= 0;

control <= 0;</pre>

check \leq 0;

xo <= 0;

yo <= 0;

busy <= 0;</pre>

rst int <= 0;</pre>

inc y <= 0;

inc x <= 0;

```

#### end

```

else begin

```

```

if(control)begin

//control <= control_1;

if(control < 13)control <= control + 1;

else if(x == x min) control <= 7;</pre>

```

```

else control <= 9;</pre>

end

else if(nt)begin

xi ff[0] <= xi;</pre>

yi ff[0] <= yi;</pre>

control <= 1;</pre>

end

if(control < 6)begin</pre>

if(xi > x max) x max <= xi;</pre>

if(xi < x min) x min <= xi;</pre>

if(yi > y_max) y_max <= yi;</pre>

if(yi < y_min) y_min <= yi;</pre>

end

else begin

if(y > yi_ff[1])top_line <= 1;</pre>

else top line <= 0;</pre>

end

case(control)

1: begin

xi_ff[1] <= xi;</pre>

yi ff[1] <= yi;

busy <= 1;

end

2: begin

xi ff[2] <= xi;

yi_ff[2] <= yi;

end

3: begin

CO <= sub ans;

end

4: begin

D0 <= sub ans;

end

5: begin

Cl <= sub ans;

inc y <= 1;

end

6: begin

D1 <= sub ans;

inc y <= 0;

end

7: begin //B = Y-Y1 B should be calculated first because it

remains the same for all values on this row

//it will return here if there is a new row with a

new y value

if(check)check <= 0;</pre>

B <= sub ans;

if(inc y)inc y <= 0;

//resets inc y back to zero to

prevent extra incrementing

if(inc x)inc x <= 0;

//resets inc x back to zero to

prevent extra incrementing

end

```

```

8:begin //BC = B*C BC should be calculated first because it

remains the same for all values on this row

BC <= mul ans;

end

9: begin //A = X-X1 It will return here if it is just a new

value of x

if(check)check <= 0;</pre>

A <= sub ans;

if(inc y)inc y <= 0;</pre>

//resets inc y back to zero to

prevent extra incrementing

if(inc x)inc x <= 0; //resets inc x back to zero to</pre>

prevent extra incrementing

end

10: begin

AD <= mul ans;

end

11: begin //B = ans

RLO <= sub ans;

end

12: begin

check <= 1; //check should be high for 2 clock cycles to</pre>

pulse po and check for valid

xo <= x;

yo <= y;

end

13: begin

if(yo >= y_max)begin

if(right triangle ^ (xo == x max)) rst int <= 1;</pre>

else if(xo == x max) rst int <= 1;</pre>

end

if((x == x max) || ~good && right triangle && ~inc y) inc y

<= 1;

if((po || ~right triangle) && ~inc y) inc x <= 1;</pre>

end

endcase

end//else begin

end//always @ (posedge clk)begin

always @(negedge clk) begin

if(inc y)begin

if((control == 6)) y <= y min;</pre>

else y <= y + 1;

x \leq x \min;

end

else if(inc x) x <= x + 1;</pre>

if(check)begin

if(good)begin

if(po)po<=0;

else begin

po <= 1;

po <= 1; // on the positive edge of po, po is set to 1

end

end//if(good)begin

```

```

else begin

po <= 0; // on the negative edge of po, po should be set to 0

end//else(~good)

end //if(check)begin

end //always @(negedge clk) begin

always@(posedge check)begin

if(((x == xi ff[0]) && (y==yi ff[0])) || ((x == xi ff[1]) && (y ==

yi ff[1])) || ((x == xi ff[2]) && (y == yi ff[2])) good <= 1;</pre>

else if((right triangle ~^ right line) || on line) good <= 1;</pre>

else good <= 0;</pre>

end

always @(*) begin //multiplier and adder modules

if(sub en) sub ans = sub op0 - sub op1;//multiplier block

if(mul en) mul ans = mul op0 * mul op1;//adder block

end

always @(*) begin

if(xi ff[1]>xi ff[0]) right triangle = 1;

else right triangle = 0;

end

always @(*) begin

if((RLO == 0) || (x == xi_ff[0]))begin

on line = 1;

right line = 0;

end

else begin

on_line = 0;

if(~top line)right line = RLO[6];

else right line = ~RLO[6];

end

end

always @(*) begin //control logic

//if(control < 13) //determines next control</pre>

// control 1 = control + 1;

//else control 1 = 7;

case(control)

0: begin

end

1: begin

end

3: begin //C0 = X2-X1

sub en = 1;

sub op0 = xi ff[1];

sub op1 = xi ff[0];

end

4: begin //D0 = Y2-Y1

sub en = 1;

sub_op0 = yi_ff[1];

```

```

sub op1 = yi ff[0];

end

5:begin

//C1 = x2-x3

sub en = 1;

sub op0 = xi ff[1];

sub op1 = xi ff[2];

end

6: begin

//D1 = Y2 - Y3

sub en = 1;

sub_op0 = yi_ff[1];

sub_op1 = yi_ff[2];

end

7: begin //B = Y-Y1

sub en = 1;

mul en = 0;

sub op0 = y;

if(~top line)sub op1 = yi ff[0];

else sub op1 = yi ff[2];

end

8: begin //BC = B*C

sub en = 0;

mul en = 1;

mul op0 = B;

if(~top line)mul op1 = C0;

else mul_op1 = C1;

end

9: begin

//A = X-X1

sub en = 1;

mul en = 0;

sub op0 = x;

if(~top line)sub op1 = xi ff[0];

else sub_op1 = xi ff[2];

end

10: begin //AD = A*D

sub en = 0;

mul en = 1;

mul_op0 = A;

if(~top line)mul op1 = D0;

else mul_op1 = D1;

end

11: begin //RLO = AB-CD

mul en = 0;

sub en = 1;

sub op0 = AD;

sub_op1 = BC;

end

12: begin

sub en = 0;

mul en = 0;

end

```

endcase end endmodule

| le Edit View Co                                        | ompile Simul           | ate Ao                                | dd W             | ave T         | ools I         | ayout             | Book                            | marks                | Wind        | ow F       | lelp                                                   |                       |                                         |

|--------------------------------------------------------|------------------------|---------------------------------------|------------------|---------------|----------------|-------------------|---------------------------------|----------------------|-------------|------------|--------------------------------------------------------|-----------------------|-----------------------------------------|

| 🖹 • 🗲 🖬 % 🎒   🐰                                        | h 🛍 🗅 🔔                | O - M                                 | t    1           | ┇┟╹╸          | ± ⊾            | ₹₹                | £   3+                          | • <del>•</del> € • ∃ | Searc       | h:         |                                                        | -                     | (1) (1) (1) (1) (1) (1) (1) (1) (1) (1) |

| ColumnLayout AllColumn                                 | 3                      |                                       | -                | - 🐴 - 🍕       | - 🖓 🖓          | 3                 |                                 |                      |             |            |                                                        |                       |                                         |

| Wave - Default                                         |                        |                                       |                  |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

| <b>·</b>                                               | Msgs                   |                                       |                  |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

| 👍 /triangle_tb/top/dk                                  | St1                    |                                       | haannaa          | າມານທານ       | ບໍ່ແມກກາກກ     | ບ່ານການການ        | ບ່ານກາດການ                      |                      | ບ່ານການການບ |            | ພ່ມກາກການແມ                                            | hononuuuu             | haaaaaa                                 |

| /triangle_tb/top/reset                                 | St0                    | մ                                     |                  |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

| 💠 /triangle_tb/top/nt                                  | St0                    |                                       |                  |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

| +                                                      |                        | -( <u>) 3'd1</u>                      |                  |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

| + /triangle_tb/top/x<br>+ /triangle_tb/top/y_mir       | 3'd6<br>3'd1           | -( <u>)) 3'd7</u><br>-( <u>)</u> 3'd0 |                  |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

| +/triangle_tb/top/y                                    | 3'd6                   | -())(3'd7                             |                  |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

| +/triangle_tb/top/xi                                   | 3'dz                   |                                       |                  |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

| +                                                      | 3'dz                   |                                       |                  |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

| +                                                      | 3'd6 3'd0 3'd6         | <u>)))) 3'd1</u>                      |                  |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

|                                                        | 3'd6 3'd3 3'd1<br>1'b1 | <u>) )) 3'd7</u>                      | 3'd2 3'd0        |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

| +/triangle_tb/top/RLO                                  | 7d2                    | -(7'd0                                |                  | 1 174         | <u> </u>       | .x x              | (- <b>7'd</b> 6 )               | ()                   | (t) x x     | l y        | (-7)                                                   | Y Y                   | x x                                     |

| <pre>/triangle_tb/top/good</pre>                       | 1'b1                   |                                       |                  |               |                |                   |                                 |                      |             |            |                                                        |                       | ألافي                                   |

| /triangle_tb/top/check                                 |                        | ٦                                     |                  | μı            |                |                   |                                 | ĽU                   |             | <u>n</u>   |                                                        | بر                    | امريا                                   |

| <pre>/triangle_tb/top/po</pre>                         | 1b1                    |                                       |                  | 1 <u> </u>    |                | <u>ш</u>          | +                               |                      |             |            |                                                        |                       |                                         |

| <pre>/triangle_tb/top/po_ /triangle_tb/top/inc_x</pre> | 1'b1<br>1'b1           |                                       | n                |               | 0              |                   |                                 | n n                  | n n         | n n        | n n                                                    | n n                   |                                         |

| /triangle_tb/top/inc_x /triangle_tb/top/inc_y          | 1b1<br>1b0             | - 0                                   |                  |               |                |                   | d L                             |                      |             |            |                                                        | الكازه                |                                         |

| <pre>/triangle_tb/top/rst</pre>                        | 1'b0                   | -                                     |                  |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

| 🚛 👍 /triangle_tb/top/xo                                | 3'd4                   | -(3'd0                                | (3'd1            | ) (3'a        | <u>11 X X</u>  |                   | <u>) 3'd1</u>                   | <u>x</u> x           | X X         | <u>x</u> x | (3'd1 )                                                |                       |                                         |

|                                                        | 3'd2                   | -{ <u>3'd0</u>                        |                  | (3'0          |                |                   | <u>) 3'd2</u>                   |                      |             |            | 3'd3                                                   |                       |                                         |

| +                                                      | 3'd4<br>3'd2           |                                       | 'd1 <u>(</u> 3'd |               | 3'd2 <u>(</u>  | <u> </u>          | <u>1 13'd2</u>                  | 1_1_                 | 11          |            | <u> (3'd2 )</u>                                        |                       |                                         |

|                                                        | 3 a2<br>1'b0           | <u>3</u>                              | 'd0              | <u>(3'd1</u>  | ┢──            |                   | <u>) 3'd2</u>                   |                      |             | (3)        | a <u>3</u>                                             |                       | (3                                      |

| <pre>/triangle_tb/top/rig</pre>                        | 1'b0                   | ц<br>п                                |                  | P             |                | ÷ ۲               | 1                               |                      |             | Ħ          |                                                        |                       |                                         |

| <pre>/triangle_tb/top/rig</pre>                        | 1'b0                   | <u> </u>                              |                  |               | F              |                   | ₽—                              |                      |             |            | <u> </u>                                               |                       |                                         |

| 🔶 /triangle_tb/top/top                                 | 1'b0                   | L                                     |                  |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

| +                                                      | 4'd9                   | -0000000                              | mmm              | 0000000       | 0000000        | 0000000           | 000000                          | mmm                  | ຫນັນນັນນ    | puuuu      | annnnn                                                 | 10000000              |                                         |

| <pre>/triangle_tb/top/su</pre>                         | 1'b1<br>7'd4           |                                       |                  |               |                |                   | ┉╵╵╼╍╸                          |                      |             |            | ╙╙╙╙                                                   |                       |                                         |

| +                                                      | 7d4                    |                                       |                  |               |                |                   | <u>#1. 1<b>702</b></u><br>YYYYY |                      |             |            |                                                        | ╡<br>┥<br>┥<br>┥<br>┥ | ▲_₩.٨_₩.4<br>† Y Y Y Y                  |

| +/triangle_tb/top/su                                   | -7'd2                  | -0007                                 |                  |               |                |                   |                                 | <u> n n</u>          | wî wî       | hi hi      |                                                        |                       |                                         |

| 🔶 /triangle_tb/top/mul                                 | 1'b0                   | ſ                                     |                  |               | பட் பட         |                   | h                               |                      |             |            |                                                        |                       |                                         |

| +                                                      | -7'd2                  | (                                     | 7'd0 )           |               | 7d1 )          | <u> </u>          |                                 |                      |             | рх – х     |                                                        |                       | <u> </u>                                |

| +                                                      | 7'd2<br>-7'd4          |                                       | 7d0 \            | 7 <u>d2 }</u> | 17d2           | + v               |                                 | d2<br>v v            | +vv-        |            | <u> </u>                                               | - Y - Y               | - v - v                                 |

| $+ - $ /triangle_tb/top/A                              | -7'd2                  | -(7'd0                                | Y do X           | 1,7'd0        | <del>† †</del> | <del>† †</del>    |                                 | Y Y                  | ╞╈╌╈        |            |                                                        |                       | <u>x x</u>                              |

| +                                                      | 7d1                    | -(7'd0                                | ,                |               | 7d1            |                   | ( <b>7</b> d2                   |                      |             |            | (-7'd4                                                 |                       |                                         |

| +                                                      | -7'd6                  | -(( <b>7'd</b> 6                      | ;                |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

| +                                                      | 7'd2                   | - <u>7d</u>                           |                  |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

| +                                                      | -7'd6<br>-7'd3         | -( <u>7'd0)</u> 7                     |                  |               |                |                   |                                 |                      |             |            |                                                        |                       | الكي                                    |

| +                                                      | -7d3<br>-7d4           | -( <u>7'd0)</u> -<br>-(7'd0           |                  | ( ) 7'd0      | y y            | y y               | 1,7d0 1                         | r y                  | r r         | - r r      | 7 <mark>'d0                                    </mark> | ry                    | 1X 1                                    |

| $\pm -4$ /triangle_tb/top/BC                           | -7'd6                  | -(7d0                                 |                  |               | ( <b>7'</b> d6 |                   | , 700 /<br>(7d                  |                      |             |            | ) -7'd24                                               |                       |                                         |

|                                                        |                        |                                       |                  |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

| Now                                                    | 42200000000 ps         | 1 I<br>DS                             | 1 1              |               | 400000         | l і і<br>)0000 ps |                                 |                      | 800000      | 0000 ps    | 1.1                                                    | 1 1                   | 12000000                                |

| Cursor 1                                               | 2640000000 ps          |                                       |                  |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

| 4                                                      |                        | •                                     |                  |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

| Library × 🖽 Project ×                                  |                        | rocesses                              | 🔹 💼 Wa           | ve × 📴        | Dataflow       | х 🖪 м             | emory List                      | × 🛺 sir              | m ×         |            |                                                        |                       |                                         |

|                                                        |                        |                                       |                  |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

| Transcript                                             |                        |                                       |                  |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

| ****** START to VER                                    | (FY the Triangel       | Renderi                               | ing Engi         | inen OPE      | RATION         | *****             |                                 |                      |             |            |                                                        |                       |                                         |

| Waiting for the rend                                   | lering operation       | of the                                | triangl          | a no ti       |                | ith.              |                                 |                      |             |            |                                                        |                       |                                         |

| (x1, y1)=(1, 0)                                        | lering operation       | OI OIC                                | Criangi          | te po_or      | 110_03 W       |                   |                                 |                      |             |            |                                                        |                       |                                         |

| (x2, y2) = (7, 2)                                      |                        |                                       |                  |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

| (x3, y3) = (1, 7)<br>Waiting for the rend              | ering operation        | of the                                | triangl          | e no ti       | nt te M        | ith:              |                                 |                      |             |            |                                                        |                       |                                         |

| (x1, y1)=(6, 1)                                        | operation              | 51 0H2                                | y1               |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

| (x2, y2)=(0, 3)                                        |                        |                                       |                  |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

| (x3, y3) = (6, 6)                                      | been generated         |                                       | 511111           |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

|                                                        |                        |                                       |                  |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

| PASS: All data have                                    |                        |                                       |                  |               |                |                   |                                 |                      |             |            |                                                        |                       |                                         |

Figure 6: The ModelSim outputs for a right facing triangle are shown above.

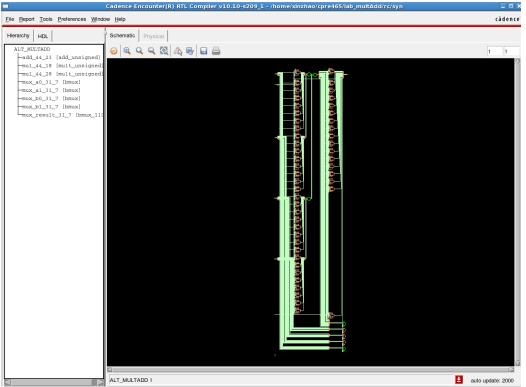

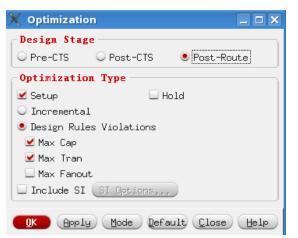

# **RTL Synthesis**

Cadence RTL Synthesizer was used to perform RTL (Register Transfer Level) synthesis. The first attempts at RTL synthesis were unsuccessful and gave multiple driver warnings. Those warnings came from setting register values under different always blocks in the Verilog code. When the synthesizer sees multiple drivers, it just assigns the register a value. Sometimes it assigns the register to be both high and low at the same time, which means that the register output is connected to both power and ground. Those problems were fixed by re-writing the Verilog code so that values were only being set under one always block.

The timing report had to be verified for a positive slack time after running synthesis. If the slack time was negative in synthesis, then it would definitely be negative in layout. A negative slack time means that a signal arrives at an input later than it needs to in order for the functionality to remain the same. A positive slack time means that the signal arrived at an input early. The goal is to get the slack time as close to zero as possible to reduce wasted power, area, and clock cycles.

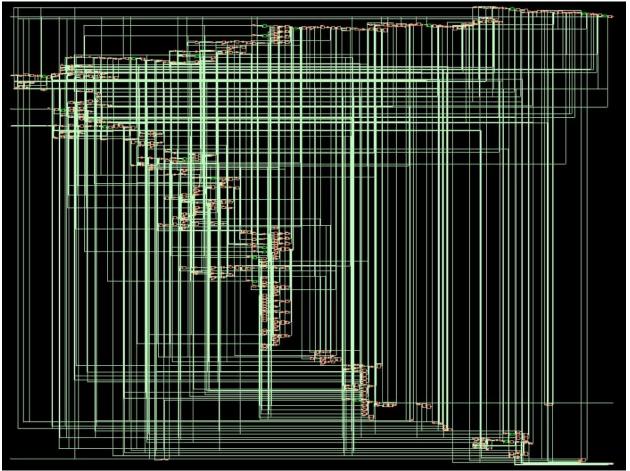

Figure 7: The image above shows the completed RTL synthesized Triangle Rendering Engine.

# Layout

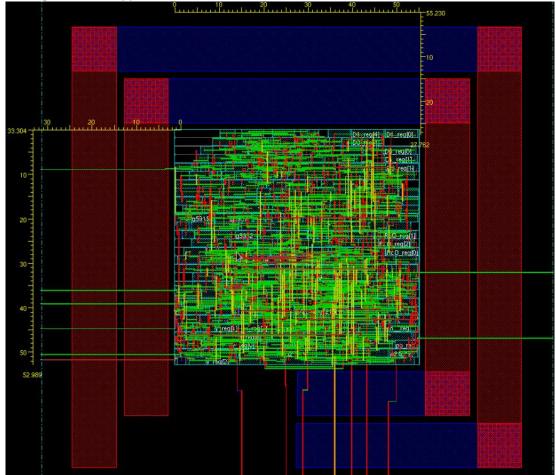

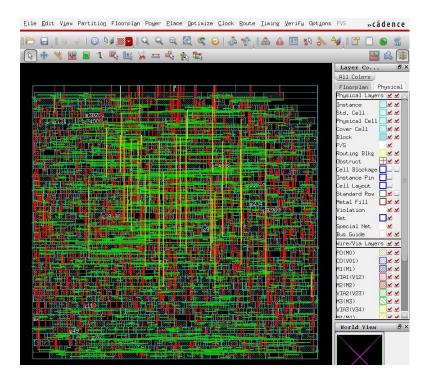

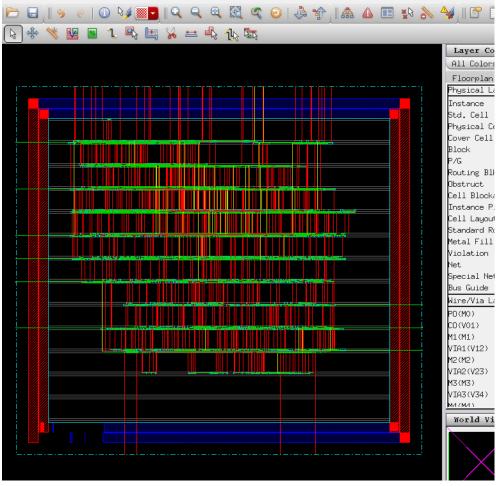

Cadence Encounter was used to perform the layout of the Triangle Rendering Engine following the instructions given in the appendix.

*Figure 8: The completed layout for the Triangle Rendering Engine is shown above.*

# Results

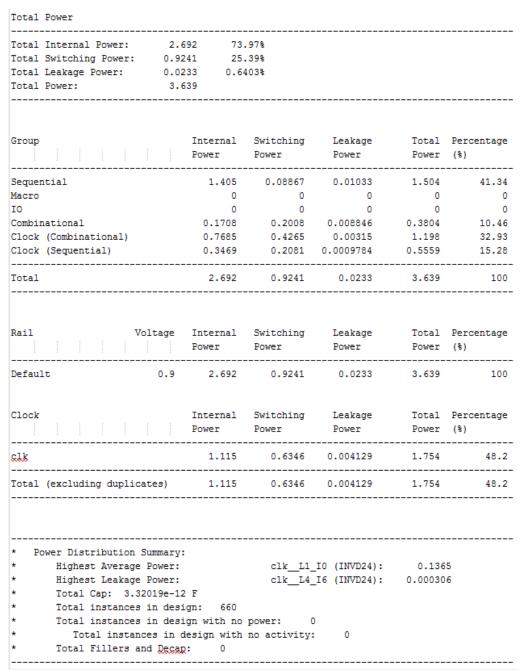

The slack time shown in Table 1 below is a negative value that can be adjusted by decreasing the clock speed or by changing the layout dimensions and core utilization. The clock period of 400 ps can be adjusted to 500 ps to ensure a positive slack time. A 500 ps clock period equates to a clock frequency of 2 GHz.

| Area                    | 0.002927 μm <sup>2</sup> |

|-------------------------|--------------------------|

| Clock Period            | 0.400 ns                 |

| Slack                   | 071 ns                   |

| Total Power Consumption | 3.639 mW                 |

Table 1: The values listed in the table above are taken after layout.

| ****************                        | **************                | ******  | *******   | ********  | #       |         |       |              |

|-----------------------------------------|-------------------------------|---------|-----------|-----------|---------|---------|-------|--------------|

| <pre># Generated by:</pre>              | Cadence Encounte              | r 10.12 | 2-s181_1  |           |         |         |       |              |

| # OS:                                   | Linux x86_64(Hos              | t ID co | 2046-06.  | ece.iasta | te.edu) |         |       |              |

| <pre># Generated on:</pre>              | Thu Dec 10 21:11              | :50 201 | .5        |           |         |         |       |              |

| <pre># Design:</pre>                    |                               |         |           |           |         |         |       |              |

| # Command:                              | <pre>report_timing &gt;</pre> | timing. | IRL       |           |         |         |       |              |

| ****************                        | ***************               | ******  | *******   | ********  | #       |         |       |              |

| Path 1: VIOLATED Cloc<br>INST/CP        | k Gating Setup Ch             | eck wit | h Pin RC: | _CG_HIER_ | INST17/ | RC_CGIC | _     |              |

| Endpoint: RC CG HIE                     | R INST17/RC CGIC              | INST/E  | (v) chec  | ked with  | leadin  | ig edge | of    |              |

| 'clk'                                   |                               |         |           |           |         |         |       |              |

| Beginpoint: y_min_reg                   | [1]/Q                         |         | (v) trig  | gered by  | leadin  | ig edge | of    |              |

| 'clk'                                   |                               |         |           |           |         |         |       |              |

| Other End Arrival Tim                   | e 0.137                       |         |           |           |         |         |       |              |

| - Clock Gating Setup                    | 0.048                         |         |           |           |         |         |       |              |

| + Phase Shift                           | 0.400                         |         |           |           |         |         |       |              |

| = Required Time                         | 0.490                         |         |           |           |         |         |       |              |

| - Arrival Time                          | 0.561                         |         |           |           |         |         |       |              |

| = Slack Time                            | -0.071                        |         |           |           |         |         |       |              |

| Clock Rise Edge                         | 0                             | .040    |           |           |         |         |       |              |

| + Clock Network                         | Latency (Prop) 0              | .178    |           |           |         |         |       |              |

| ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ | ival Time 0                   |         |           |           |         |         |       |              |

|                                         | tance                         |         |           | L Cell    |         |         |       |              |

| T                                       |                               | I       |           | I         | I       | _       | Time  | Time         |

| <br>  y_min_reg[1]                      |                               |         |           | +<br>     |         |         |       | +<br>  0.147 |

| <pre>y_min_reg[1]</pre>                 |                               | CP ^    | -> Q v    | DFQD4     | 1       | 0.143   | 0.361 | 0.290        |

| g7363                                   |                               | A2 v    | -> ZN ^   | OAI211D   | 2       | 0.037   | 0.398 | 0.327        |

| g7362                                   |                               | A1 ^    | -> ZN v   | ND2D1     | 1       | 0.040   | 0.438 | 0.367        |

| g7361                                   |                               | A v -   | -> CON ^  | FCICOND   | 1       | 0.073   | 0.511 | 0.440        |

| g5975                                   |                               |         |           |           |         |         |       | 0.490        |

| RC_CG_HIER_INS                          | T17                           | enabl   | le v      | RC_CG_M   | OD_17   |         | 0.561 | 0.490        |

|                                         | T17/RC_CGIC_INST              |         |           |           |         |         |       |              |

| +                                       |                               |         |           |           |         |         |       |              |

Figure 9: The after layout timing report is shown above.

```

*_

_____

Encounter 10.12-s181_1 (64bit) 07/28/2011 22:52 (Linux 2.6)

*

Date & Time: 2015-Dec-12 16:30:22 (2015-Dec-12 22:30:22 GMT)

*

*_

_____

*

Design: triangle

Liberty Libraries used:

*

./../libdir/tcbn65gpluswc.lib

*

Power Domain used:

*

User-Defined Activity : N.A.

Activity File: N.A.

*

Hierarchical Global Activity: N.A.

*

*

Global Activity: N.A.

*

Sequential Element Activity: N.A.

*

*

Clock Gates Output Activity: N.A.

*

*

Clock Gates Enable Activity: N.A.

*

Primary Input Activity: 0.200000

*

*

Power Units = 1mW

*

Time Units = 1e-09 secs

report_power -outfile Layout_power -sort total

_____

```

Figure 10: The after layout power report is shown above.

# Conclusion

The hardest part of this project was understanding how to determine if the points were in the triangle and getting the timing correct to report those values. Since for loops are generally not synthesizable, counters were used to loop through the rows between y1 and y3 and the columns between x1 and x2. We also learned early on that there is not a direct synthesizable division function. Dr. Chu pointed out that the equations could be re-written in such a way that they only used subtraction and multiplication which are synthesizable. After the Verilog code was tested for functionality, problems were identified with multiple drivers when synthesizing the circuit. The Verilog code was re-written to solve the problems as stated earlier in the report.

# Appendix

#### ModelSim

#### Use the following commands in the terminal to launch ModelSim.

source /remote/Xilinx/12.2/settings64.sh

export PATH=\$PATH:/remote/Modelsim/6.5c/modeltech/linux\_x86\_64/

export LM LICENSE FILE=1717@io.ece.iastate.edu:27006@io.ece.iastate.edu

## **RTL Synthesis Instructions**

# **Tutorial for Cadence RTL Compiler**

1. <u>Setting up:</u> Please download the file rc.rar and decompress it to a newly created project directory. Go to the folder named "rc". It should have 3 folders, named libdir, rtl and syn.

• libdir: contains the library files the tool will use.

• rtl: contains the Verilog codes needed to be synthesized. Please copy your Verilog file which already made in Lab 1 to this folder and renamed it as "ALT\_MULTADD.v". Please do not include your test bench file because that is for simulation only.

• syn: contains run\_dir (which holds the results of running synthesis) and scripts (which holds the scripts for running synthesis). More importantly, in the scripts folder, there are 3 files. They are:

1) design.sdc: contains the constraints you want to add to the design. They are already set. Please note in the Verilog file you made in Lab 1, if you changed the port names that are defined in the Lab 1 instruction, you need to modify this file to adapt to your port names.

2) read\_rtl.tcl: is a script used to read in your Verilog file. Please note if you have more than one Verilog files to be read in, you need to add lines in this file to read all your Verilog files.

3) run\_synth.tcl: is the top level script to drive the synthesis tool. This file will use the other 2 files.

2. <u>Starting RTL Compiler</u>: Open a new terminal. In the newly created project directory, type "source

/etc/software/edi" and hit Enter. Go to the syn directory. Then type "rc –gui" to invoke RTL Compiler, our synthesis tool from Cadence.

3. <u>Performing synthesis:</u> You can perform synthesis by running the script that is already made for you. Go to File ---> Source Script from the File menu of the Menu Bar. Select the run\_synth.tcl in the "scripts" folder. Click OK. The tool will do the synthesis job for you. Just wait for the result. A gate level schematic will be shown in the gui window as below:

Please find the log file in the "syn" folder, and search for the keyword "error" to make sure there is no error happened during the synthesis.

4. <u>Timing report:</u> You can check the timing report by going to Report ---> Timing ---> Worst Path. (You may also generate a plain text version of the timing report by type "report timing" in the command window.)

| HTML<br>Endpi<br>icc_reg[7]/D |      |                 | tailed Timing Re | port          |           |            |              | - 0 |

|-------------------------------|------|-----------------|------------------|---------------|-----------|------------|--------------|-----|

|                               | oint | nt acc_reg[7]/D |                  |               |           |            |              |     |

| cc_reg[7]/D                   |      | Slack (ps)      |                  | Rise Stew (pa | 0         | Fall       | Slew (ps)    |     |

|                               |      |                 | 17320            |               | 60        |            |              | 50  |

| ۹                             |      |                 |                  |               |           |            |              |     |

|                               | Pin  | Туре            | Fanout           | Load (IF)     | Slew (ps) | Delay (ps) | Arrival (ps) |     |

| lock clk)                     |      | launch          |                  |               |           |            | 0.0          |     |

| cc_regi0/CLK                  |      |                 |                  |               | 0.0       |            | 0.0          |     |

| :c_reg 0//0                   |      | DFFPO5X1        | 3                | 61.1          | 117.4     | 257.6      | 257.6        |     |

| 59/8                          |      |                 |                  |               |           | 0.0        | 257.6        |     |

| 59/Y                          |      | NAND2X1         | 2                | 75.5          | 213.6     | 184.7      | 442.3        |     |

| 50/A                          |      |                 |                  |               |           | 0.0        | 442.3        |     |

| 50/Y                          |      | OAI21X1         | 1                | 92.2          | 185.0     | 169.0      | 612.1        |     |

| 46/A                          |      |                 |                  |               |           | 0.0        | 612.1        |     |

| 46/YC                         |      | FAX1            | 1                | 92.2          | 201.8     | 335.6      | 947.7        |     |

| 43/A                          |      |                 |                  |               |           | 0.0        | 947.7        |     |

| 43/YC                         |      | FAX1            | 1                | 92.2          | 201.0     | 336.3      | 1206.0       |     |

| i4D/A                         |      |                 |                  |               |           | 0.0        | 1286.0       |     |

| 40/VC                         |      | FAX1            | 1                | 92.2          | 201.8     | 338.3      | 1624.3       |     |

| 37/A                          |      |                 | -                |               |           | 0.0        | 1624.3       |     |

| 37/YC                         |      | FAX1            | 1                | 92.2          | 201.0     | 338.3      | 1962.6       |     |

| 34/A                          |      |                 |                  | 01.1          | 201.0     | 0.0        | 1962.6       |     |

| 34/YC                         |      | FAX1            | 1                | 42.9          | 120.8     | 260.8      | 2223.4       |     |

| 132/A                         |      | r ooi           |                  | 46.0          | 160.0     | 0.0        | 2223.4       |     |

| 32/Y                          |      | XOB2X1          | 1                | 22.4          | 111.7     | 131.6      | 2355.0       |     |

|                               |      | AUREAT          |                  | 22.4          |           | 0.0        | 2355.0       |     |

| 30/B                          |      | AUG000/4        |                  | 42.0          | 62.2      |            |              |     |

| i30/V                         |      | NOR2X1          | 1                | 13.0          | 57.7      | 65.2       | 2420.2       |     |

| :c_reg[7]/D                   |      | DFFPOSX1        |                  |               |           | 0.0        | 2420.2       |     |

| c_reg[7]/CLK                  |      | setup           |                  |               | 0.0       | 252.1      | 2672.3       |     |

| lock clk)                     |      | capture         |                  |               |           |            | 20000.0      |     |

| T                             |      |                 |                  |               |           |            |              |     |

Note that for the report in the diagram above, the "Slack time" is 17328ps. Since it is positive, the tool is telling you that the signal arrives at the FF on the right much earlier than necessary. This means that the circuit can work with a much higher clock frequency. If you want your design to run at a higher frequency, you need to change the design.sdc file. There is a constraint to set up the clock period. Change it to what you want. And re---run the whole flow again.

5. <u>Area report:</u> For the area report, go to Report ---> Netlist ---> Area. (You may also generate a plain text version of area report by type "report area" in the command window.) Check the total area. If we ask the synthesis tool to produce a faster circuit, this value is likely to increase.

| Ŷ                                                                                                                                                                  |                      | Re                  | port Area        |                       |                   | - 11 3  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------|------------------|-----------------------|-------------------|---------|

| Generated by: Encounter(R)<br>Generated on: Oct 25 2010<br>Module: accu<br>Technology library: osu025_<br>Operating conditions: typical<br>Wireload mode: enclosed | 14:00:42<br>stdcells | 08_1 (Jul 29 2008)  |                  |                       |                   |         |

| Instance<br>accu                                                                                                                                                   | Collin<br>32         | Cot Area<br>4401.00 | Not Area<br>0.00 | Toto: Area<br>4401.00 | Wrotoad<br>(nane> | WL Flag |

| si                                                                                                                                                                 |                      | HTML                | Close            | Help                  | _                 | >       |

6. <u>Power report:</u> To report the power, go to Report ---> Power ---> detailed report. (You may also generate a plain text version of power report by type "report power" in the command window.)

The power, timing and area reports are also generated by scripts and are stored in the run\_dir folder. Please check it.

## **Encounter Instructions**

# Instructions on Placement and Routing by Encounter

1. Go to "run\_dir" folder, source /etc/software/edi Type "usr/local/cadence/EDI101/bin/encounter" to start.

2. In the command window, type "set rda\_Input(ui\_pwrnet) {VDD}" and "set rda\_Input(ui\_gndnet) {VSS}". By using these 2 commands, we set two nets VDD and VSS.

3. Select File  $\rightarrow$  Import RTL In the "Logical" tab:

- Set "Verilog Files" to your synthesis result of Lab 4. It should be in "rc/syn/run\_dir" of your Lab 4 directory. *Please double-click the file to select*.

- For "Top Level", select "Auto Assign".

- Set "Max Libs" to the "tcbn65gpluswc.lib", which is located in "encounter/libdir/lib" folder.

• Set "Constraint Files" to the .sdc file which is generated in your Lab 4 and should be located in "rc/syn/run\_dir" directory of your Lab 4. It describes the constraint settings of your Lab 4. The RTL compiler outputted them as a file for Encounter to use.

In the "Physical" tab:

1. Set "LEF Files" to "tcbn65gplus\_8lmT2.lef", which is located in "encounter/libdir/lef". It contains the geometry information of the standard cells, which is needed during placement and

routing.

Click "OK" to submit. Now, we finished specifying the inputs for placement and routing.

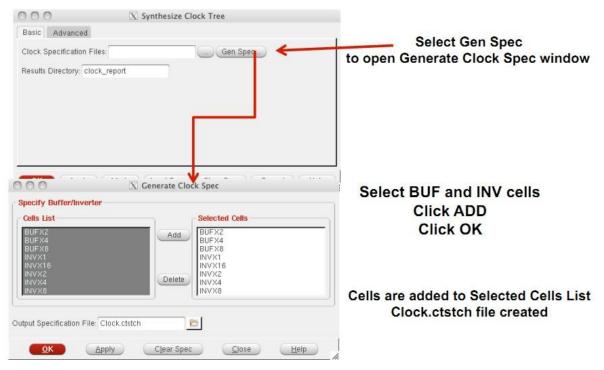

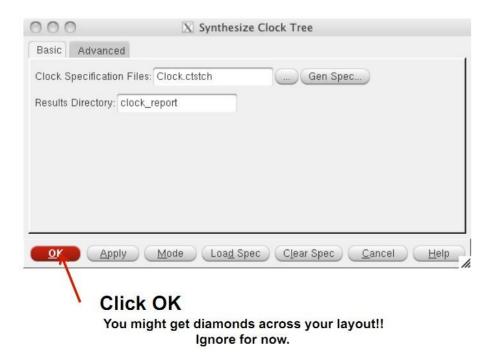

4. Select File  $\rightarrow \rightarrow$  RTL Synthesis

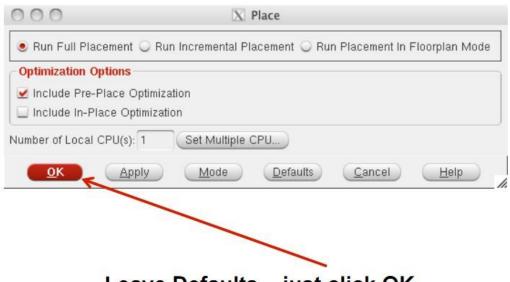

Select "Proceed with Placement", and then click "OK". Ignore the warning about not specifying floorplan or def file.

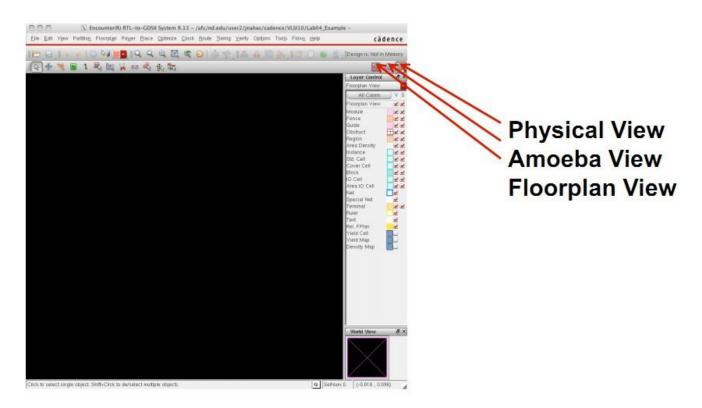

Now, please select the physical view to display your layout. You may need to press "F" to see the whole circuit.

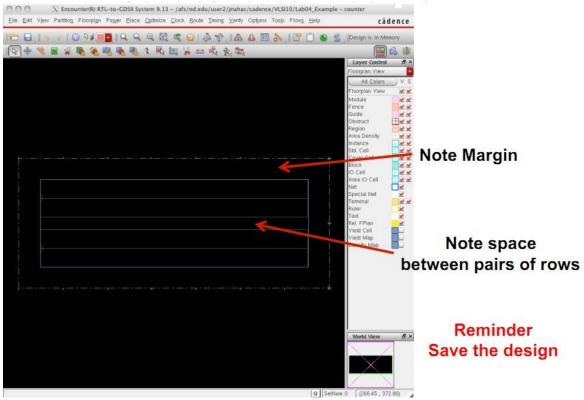

#### 5. Select Floorplan $\rightarrow$ Specify Floorplan

Set the parameters and options for both "Basic" and "Advanced" tabs using the values as shown in the figures below. Please note that these parameters will affect your layout result.

| Design Dimensions                                                        |            |                   |              |                 |

|--------------------------------------------------------------------------|------------|-------------------|--------------|-----------------|

| Specify By: 🖲 Size 🔾 Die/IO/Core Coor                                    | rdinates   |                   |              |                 |

| 🥑 Core Size by: 🖲 Aspect Ratio:                                          | Ratio (H/W | ):                | 7 8.         | Aspect Ratio    |

|                                                                          | 🥑 C        | ore Utilization:  | 0.699881     |                 |

|                                                                          | 00         | Cell Utilization: | 0.699881     | Can be adjusted |

| O Dimension:                                                             | Width      | n (               | 252.9        | if desired      |

|                                                                          | Heigh      | t:                | 108.0        |                 |

| Die Size by:                                                             | Width      | 1:                | 314.1        |                 |

|                                                                          | Heigh      | t                 | 168.0        | 30 micron       |

| Core Margins by: 🖲 Core to IO Bound                                      |            |                   |              |                 |

| Core to Die Bound                                                        |            |                   |              | margins add     |

| Core to Left:                                                            | 30         | Core to Top:      | 30.0         | Left            |

| Core to Right:                                                           |            | Core to Bottom:   | 30.0         |                 |

| Die Size Calculation Use: O Max IO H<br>Floorplan Origin at: O Lower Lef |            |                   |              | Right           |

| Floorphan origin at                                                      | Conter O   | Center            | Unit: Micron | Тор             |

|                                                                          |            |                   |              | Bottom          |

Click Apply to see how floorplan changes affect layout on main screen

| 000                       | X Specify Floorplan        |                         |

|---------------------------|----------------------------|-------------------------|

| Basic Advanced            |                            |                         |

| Standard Cell Rows        |                            |                         |

| Double-back Rows:         | 🕨 Bottom Row Orient: 🔵 📼 🔊 |                         |

| Row Spacing: 18 🗲         | Enr Every 2 Row            |                         |

| Site: core > Row Hei      | ght: 27.0                  | 18 micron spacing added |

| Allow Overlapping Sa      | me Site Rows               | ie inie opaenig aaaea   |

| IO Specifications         |                            |                         |

| Bottom IO Pad Orientation | r. 🔲 R0)                   |                         |

| Use I/O Rows for I/O P    | lacement                   |                         |

|                           |                            |                         |

|                           |                            |                         |

|                           |                            | Click OK when don       |

| ок 🗲                      | Apply Cancel               | Help                    |

Then the placement region will be displayed:

6. Select Power  $\rightarrow$  Power Planning  $\rightarrow$  Add Ring

Set the parameters and options for "Basic" tab using the values as shown in the figure below.

| Add Rings  asic Adaranced Via Generation  Net(s): VDD VSS  Ring Type  Core ring(s) contouring  Along VO boundary  Exclude selected objects Block ring(s) around Each field Selected power domain/fences/reefs Each selected block and/or group of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks and/or groups of core rows Clusters of selected blocks a | VDD VSS               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Net(s) VDD VSS<br>Ring Type<br>Core ring(s) contouring<br>Around core boundary<br>Core ring(s) around<br>Core ring(s) around<br>Each block<br>Each block<br>Each reef<br>Selected power domain/fences/reefs<br>Each selected block and/or group of core rows<br>Clutters of selected blocks and/or groups of core rows<br>Clutters of selected blocks                                                                                                                                                                                                                                                                                                                     | VDD VSS               |

| Ring Type         Core ring(s) contouring         Around care boundary         Exclude selected objects         Block ing(s) around         Each block.         Block ing(s) around         Each block.         Selected power domain/fences/reefs         Selected power domain/fences/reefs         Custers of selected block and/or groups of core rows         With shared ring edges         User defined coordinates:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | VDD VSS               |

| Ring Type         Core ring(s) contouring         Around care boundary         Exclude selected objects         Block ring(s) around         Each islock         Each reaf         Selected power domain/frances/reafs         Each selected block and/or group of core rows         Cluster of selected blocks and/or groups of core rows         With shared ring edges         User defined coordinates:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                       |

| Around core boundary     Along VO boundary     Exclude selected objects     Block fing(s) around     Each block.     Each reef     Selected power domain/fences/reefs     Each selected block and/or groups of core rows     Clusters of selected blocks and/or groups of core rows     With shared ring edges     User defined coordinates:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                       |

| Around care boundary     Along VO boundary     Exclude selected objects     Block ring(s) around     Each block     Each reef     Selected power domain/Tences/reefs     Each selected block and/or group of core rows     Clusters of selected blocks and/or groups of core rows     With shared ring edges     User defined coordinates:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                       |