Successive Approximation Register Analog to Digital Converter (SAR ADC or A/D)

Intro:SAR is frequently used for medium-to-high-resolution applications with sample rates under 5 Msps.The SAR architecture allows for high-performance, low-power ADCs to be packaged in small form factors for today’s demanding applications.

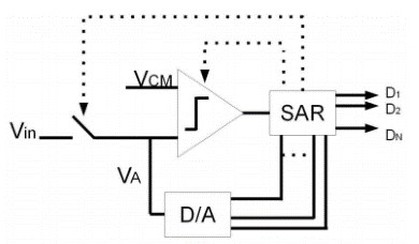

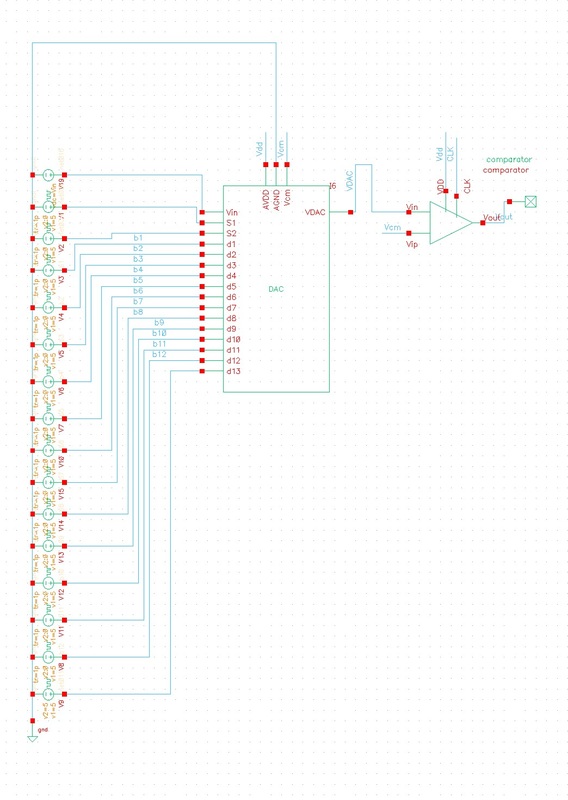

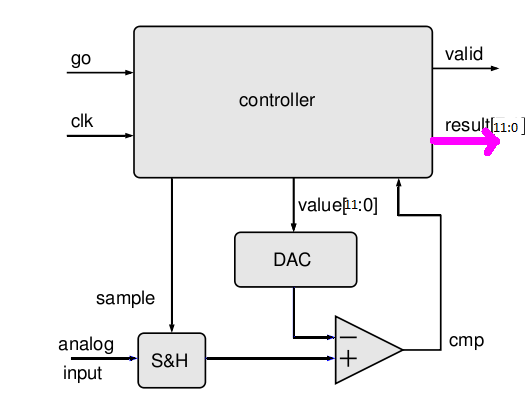

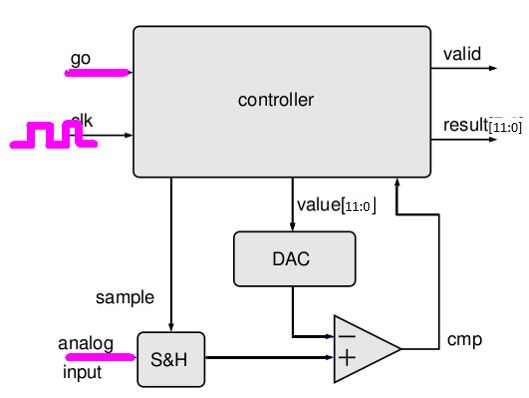

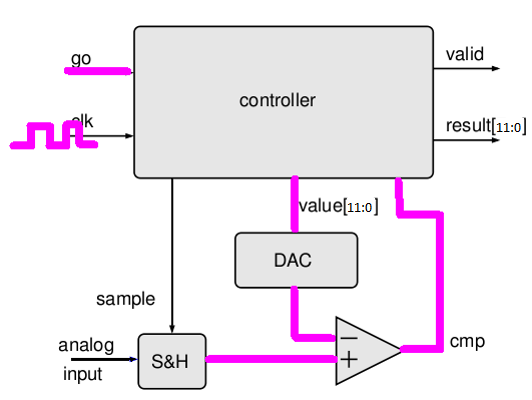

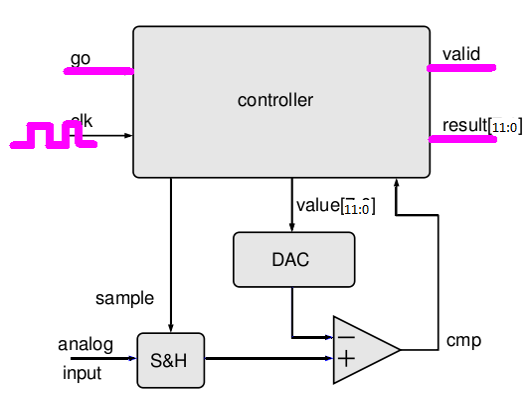

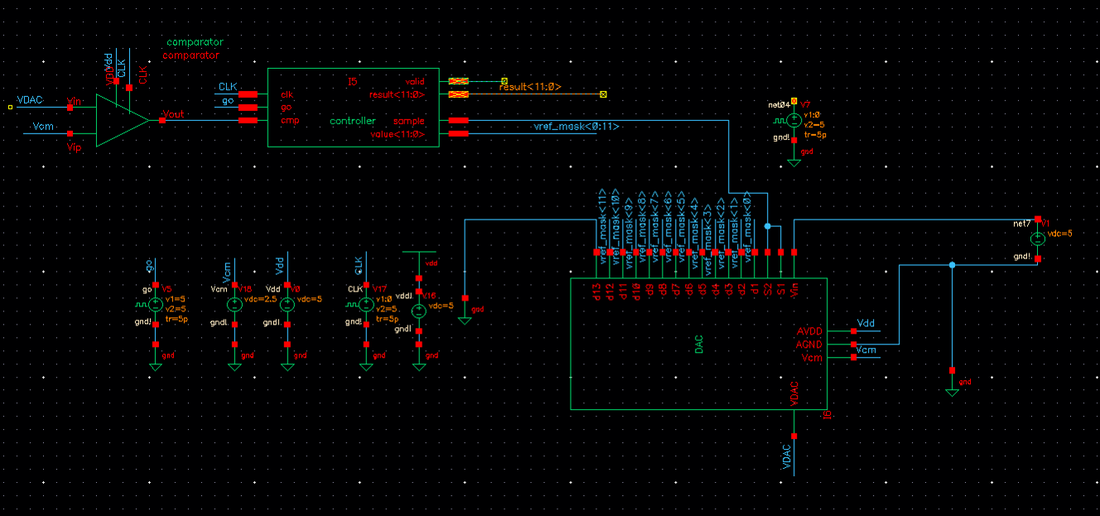

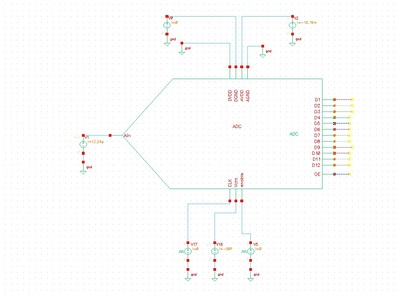

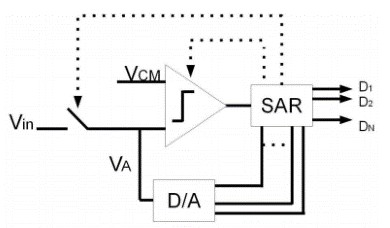

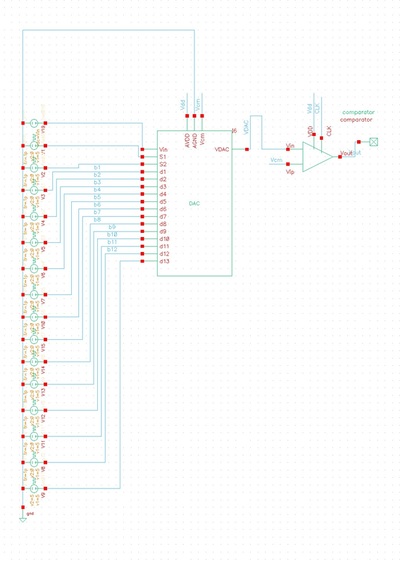

Basic Concept:A SAR ADC uses a successive test algorithm to determine the voltage at an input node. As seen in the figure to the right, this includes a Digital to Analog converter(DAC). The DAC generates a reference voltage for a comparator which will test whether the input voltage is higher or lower than the voltage at the output of the DAC. The output of the comparator determines the next digital output of the SAR ADC iteration cycle. This process repeats until all the bits in the 12-bit value corresponding to the voltage that is sent to the DAC are set.

|

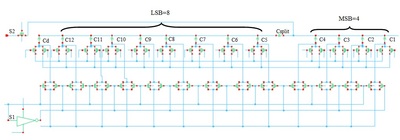

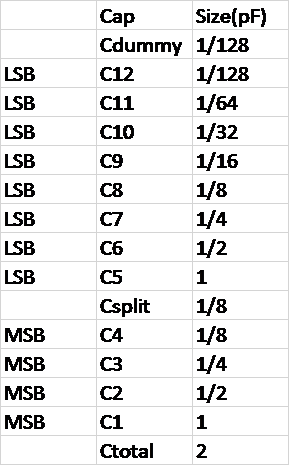

The Digital to Analog Converter

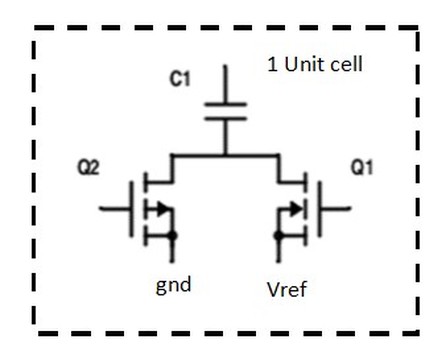

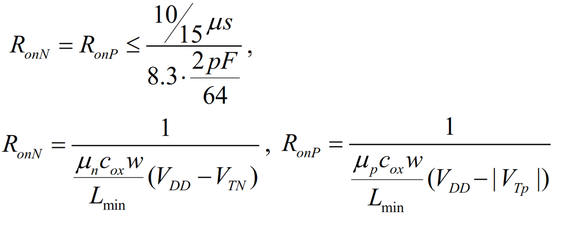

DAC Switch Sizing

|

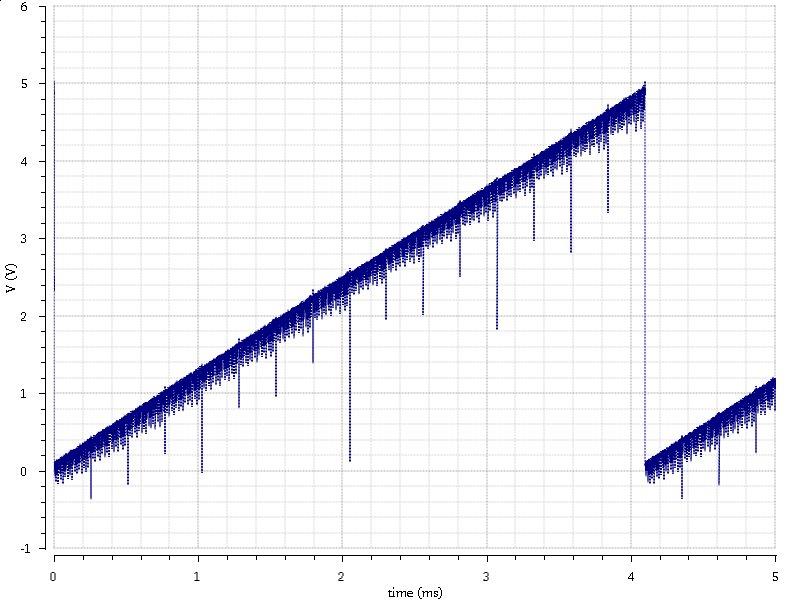

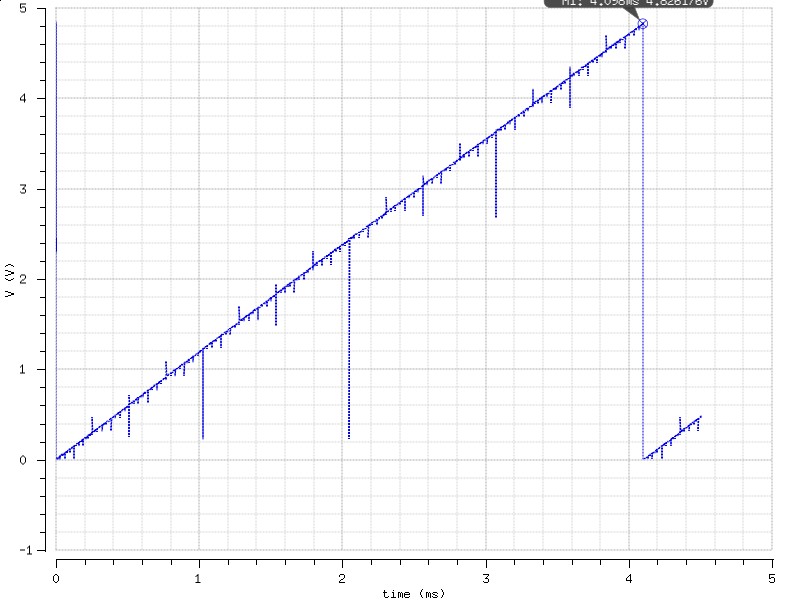

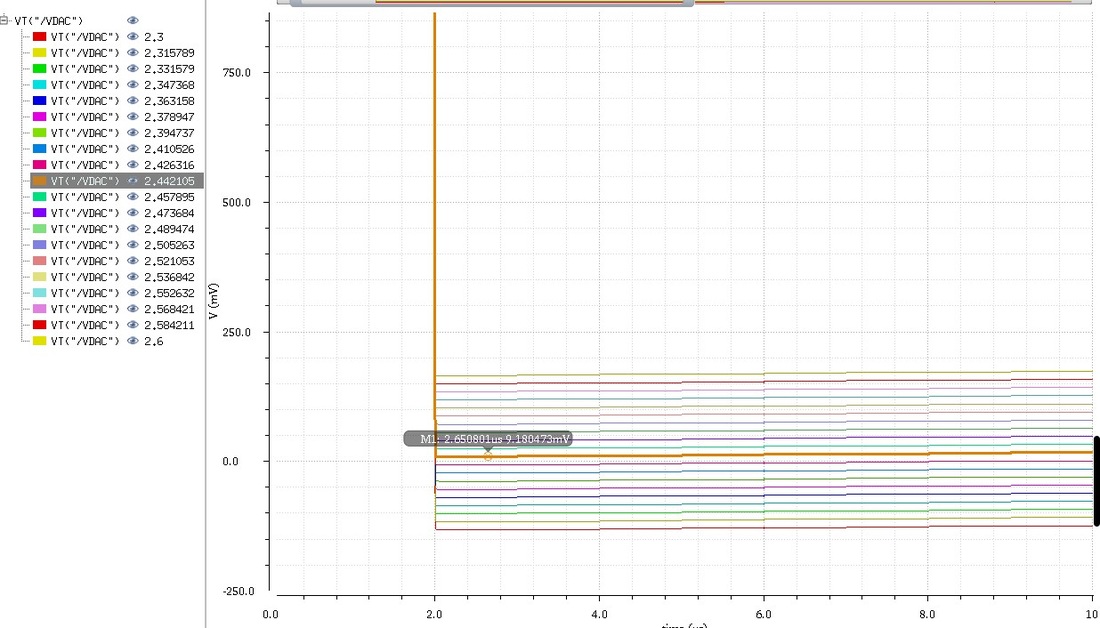

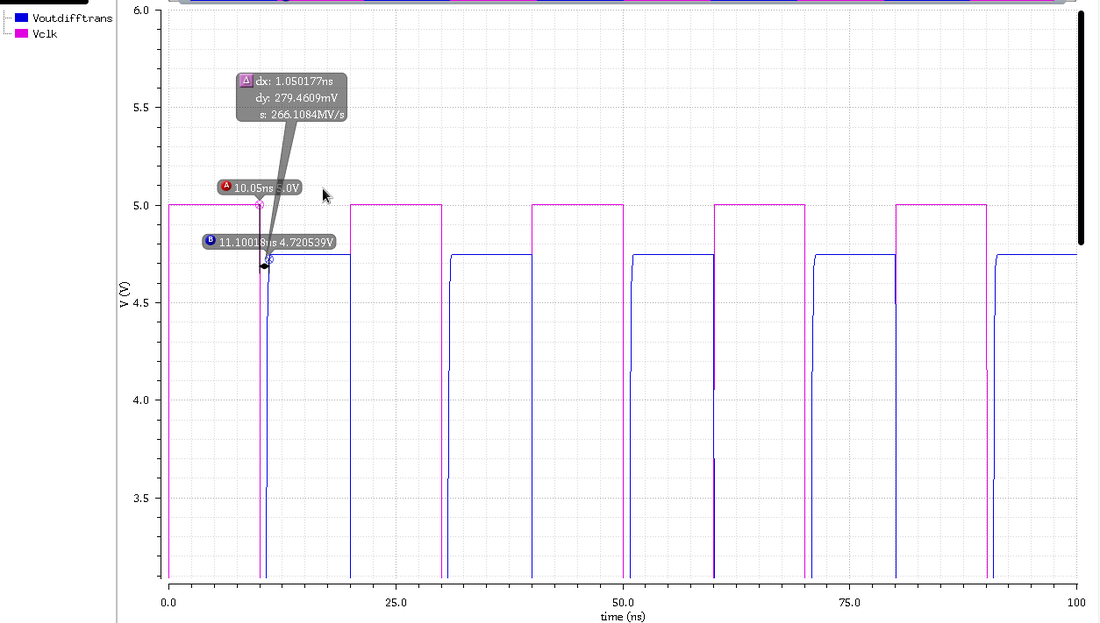

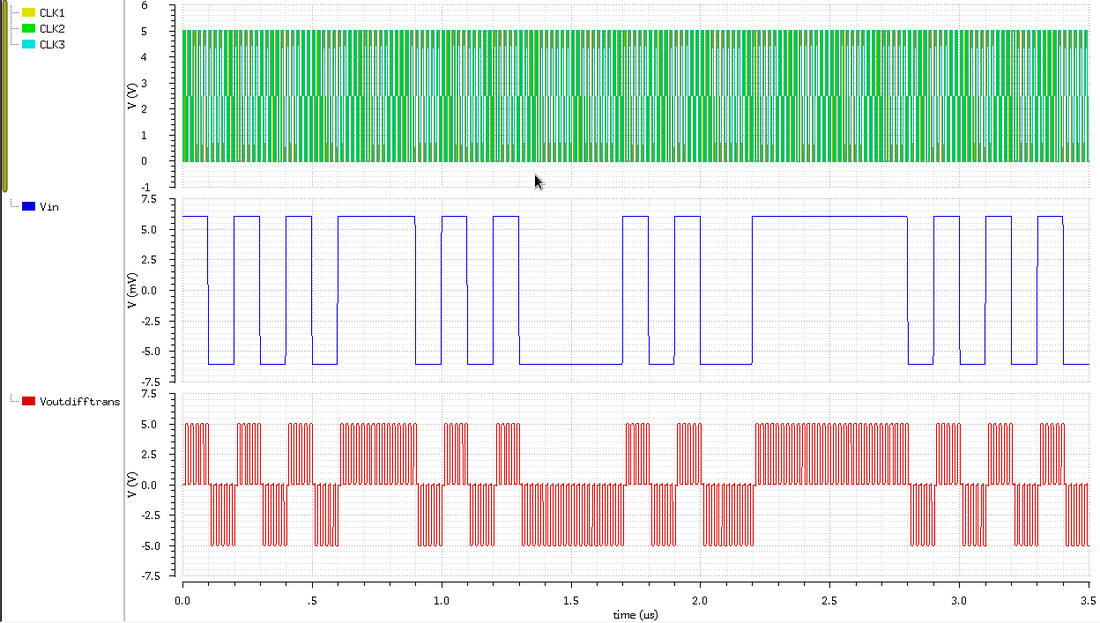

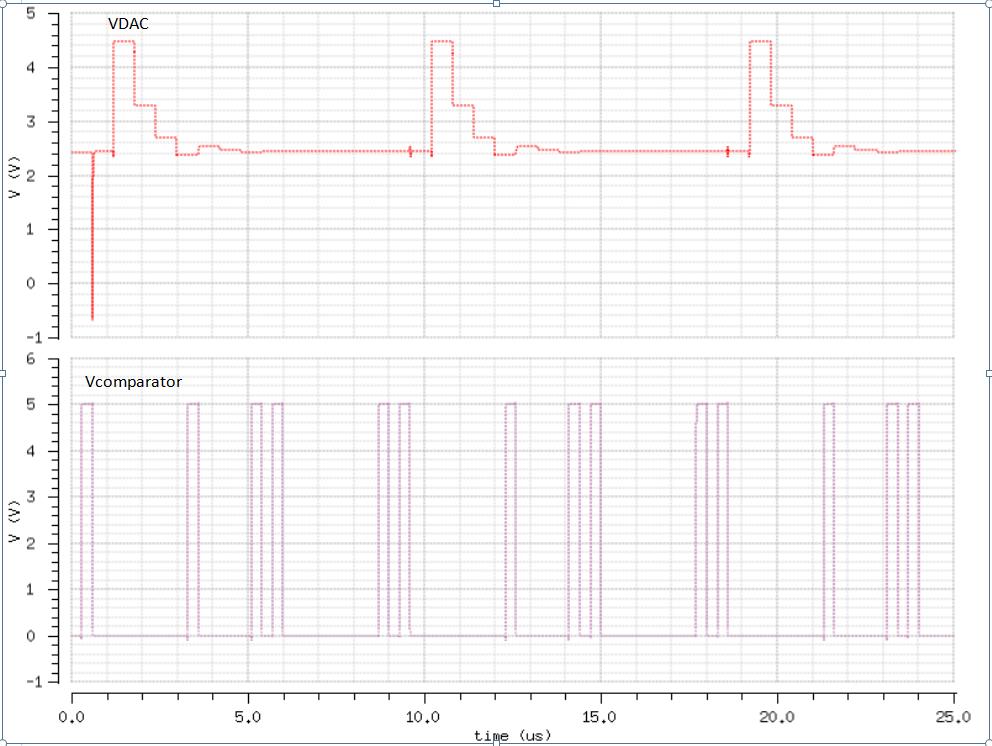

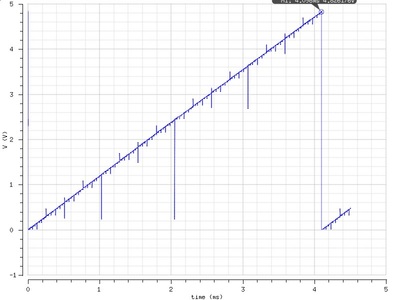

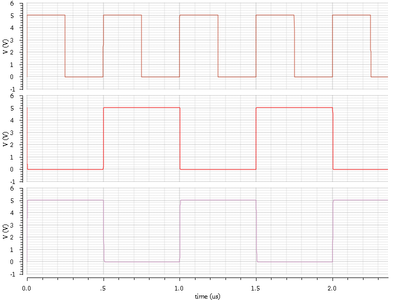

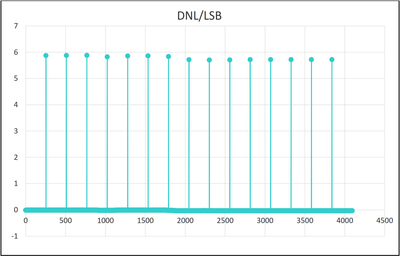

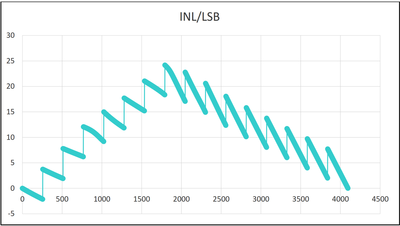

As we can see, before we size the switches, in the figure to the left above, there were multiple glitches occurring on the line. But after we sized our switches, the glitches were reduced effectively. We were confused why the DAC only measured 4.8V instead of our expected 5V. Another problem needing to be mentioned here is that there is an offset on the DAC. We reduced the offset temporarily by finding a good common mode voltage Vcm for DAC. We set Vcm as variable and swept the voltage and plotted it in the figure to the left.

As you can see, the best Voffset occurs when Vcm is 2.44V, at which we have the smallest offset of 9.18mV. But changing V to adjust the offset is not the best way to eliminate offset. Instead, we chose to use offset cancellation to cancel the offset. The offset cancellation is discussed in the Comparator section later on this page. |

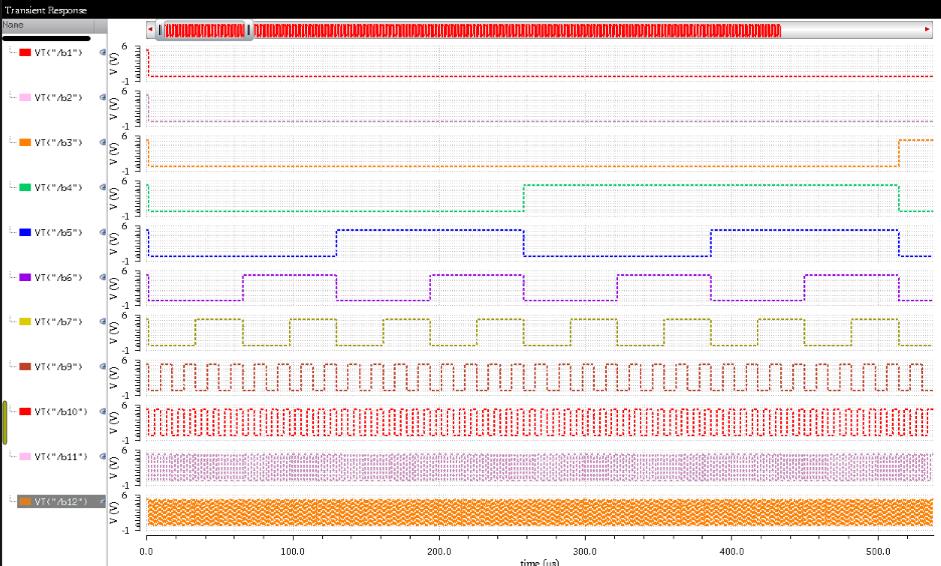

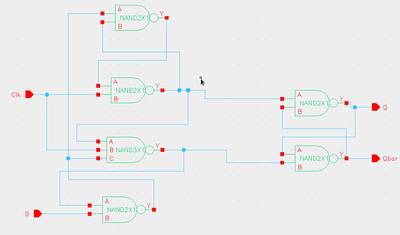

Synchronous Complementary Output D Flip-Flop

|

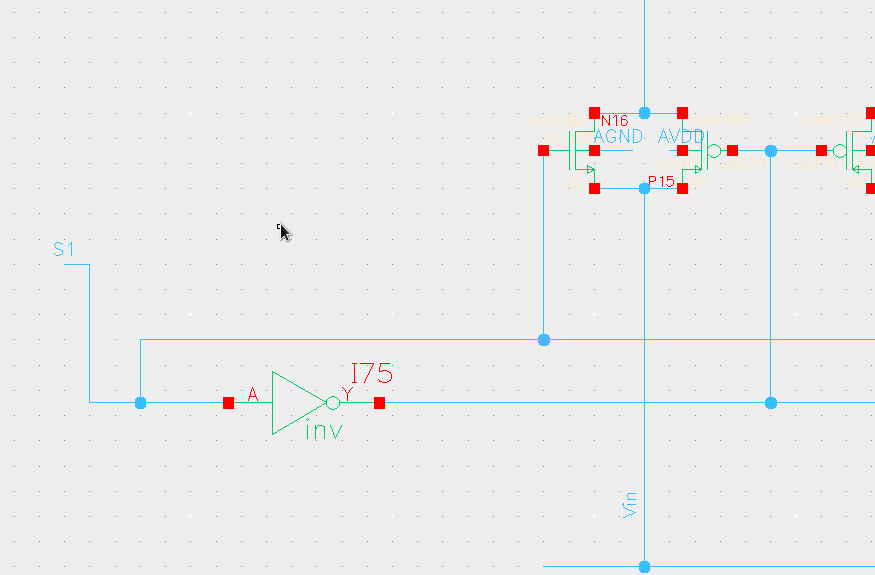

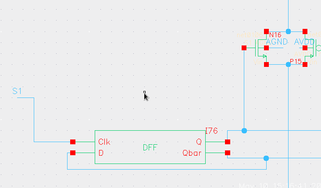

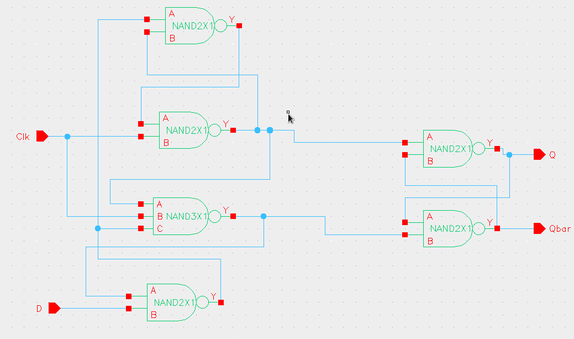

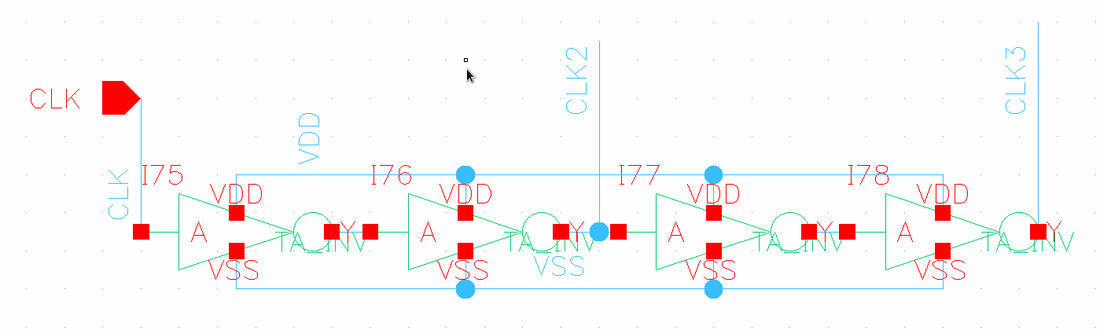

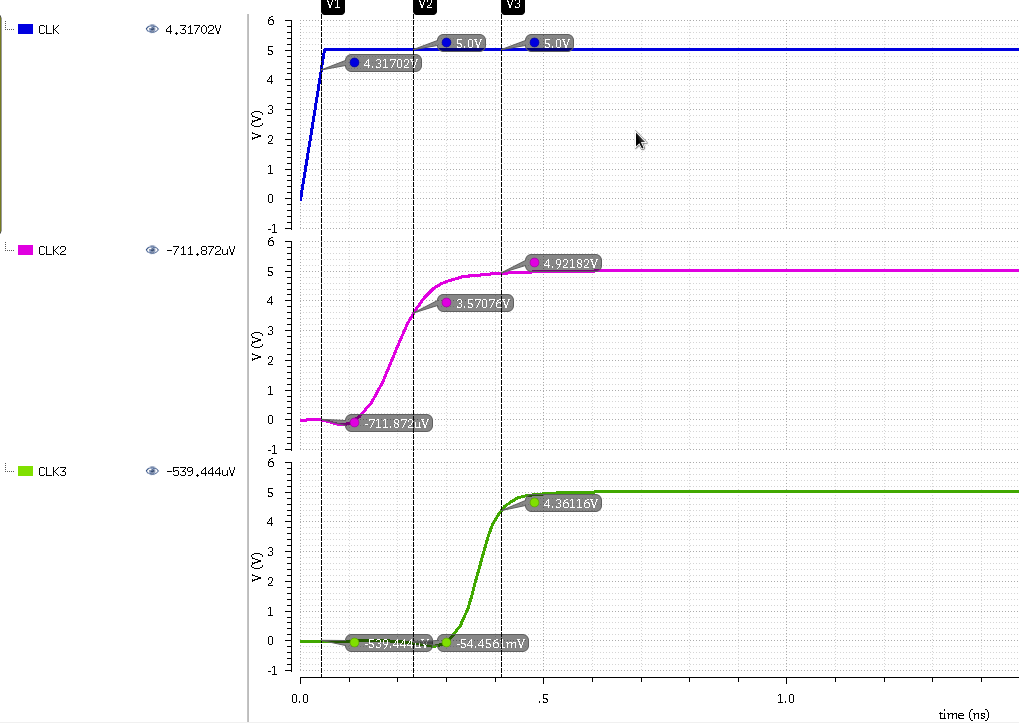

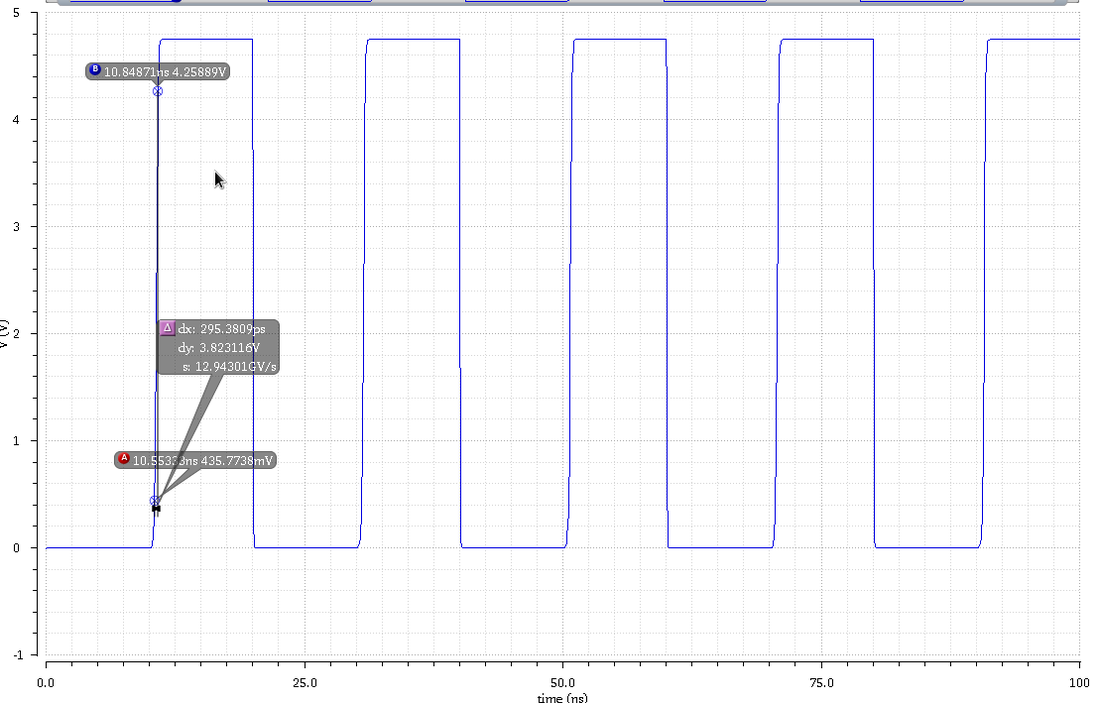

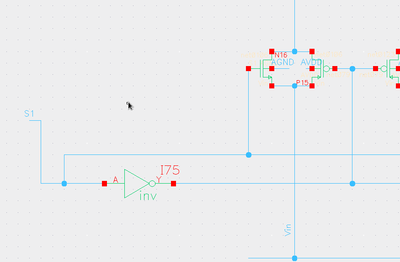

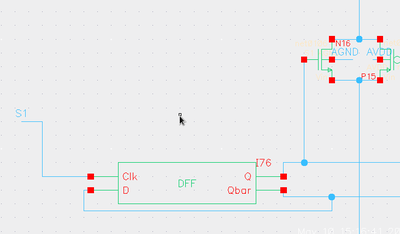

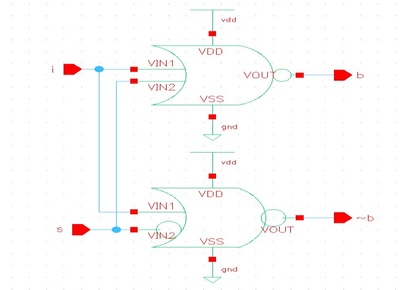

This is the original design of our transmission gate signal driver. The difference in clock edge from the input versus the inverter may cause the PMOS transistor of the transmission gate to be switched at a later time than the NMOS. To prevent this from happening, we decided to try and use a synchronous D flip-flop. The DFF in the standard libraries don’t provide a true synchronous output that we need. So we had to design a DFF at the gate level.

|

|

In order for the switches to work correctly and synchronously, a synchronous input is required. a synchronous D-Flip flop should be sufficient to provide a synchronous complimentary switch signal.

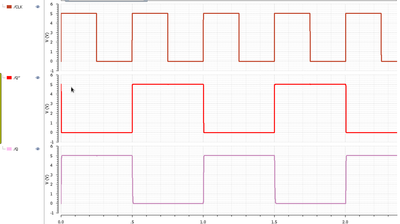

Connected as a clock divider, we used the synchronous DFF to generate our complimentary signals for the switches. |

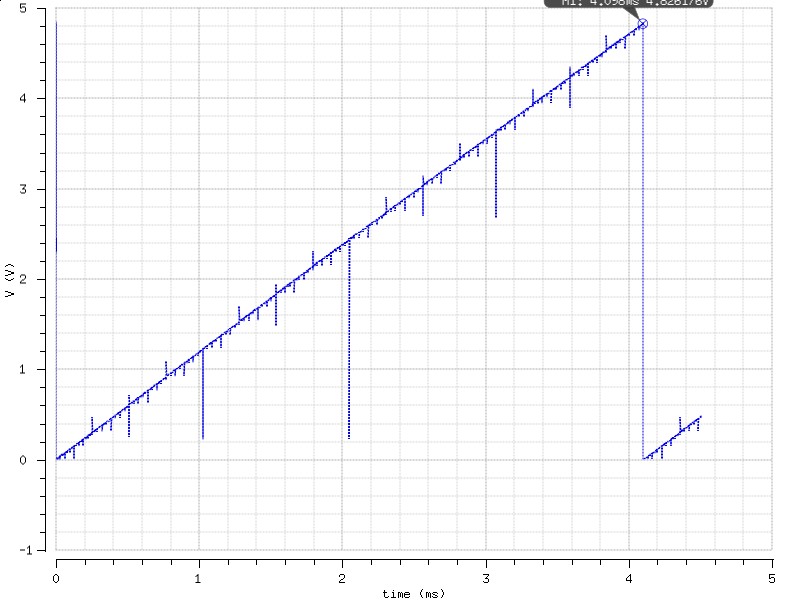

DAC Performance

Comparator

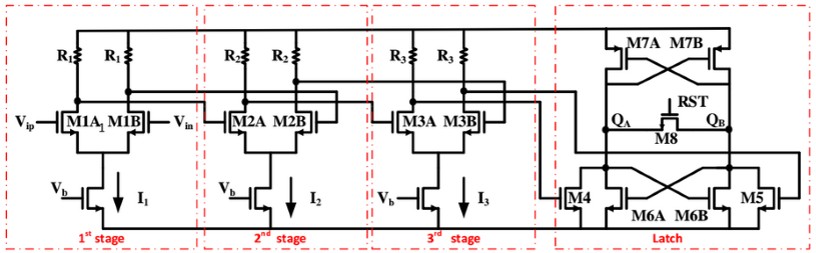

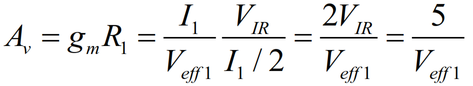

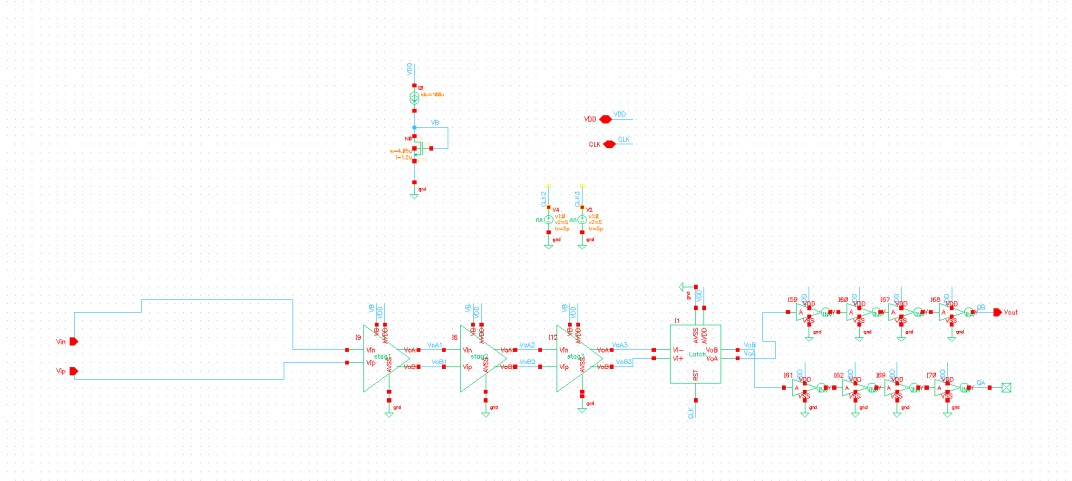

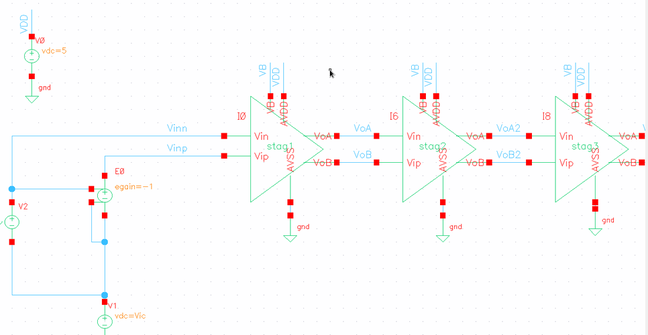

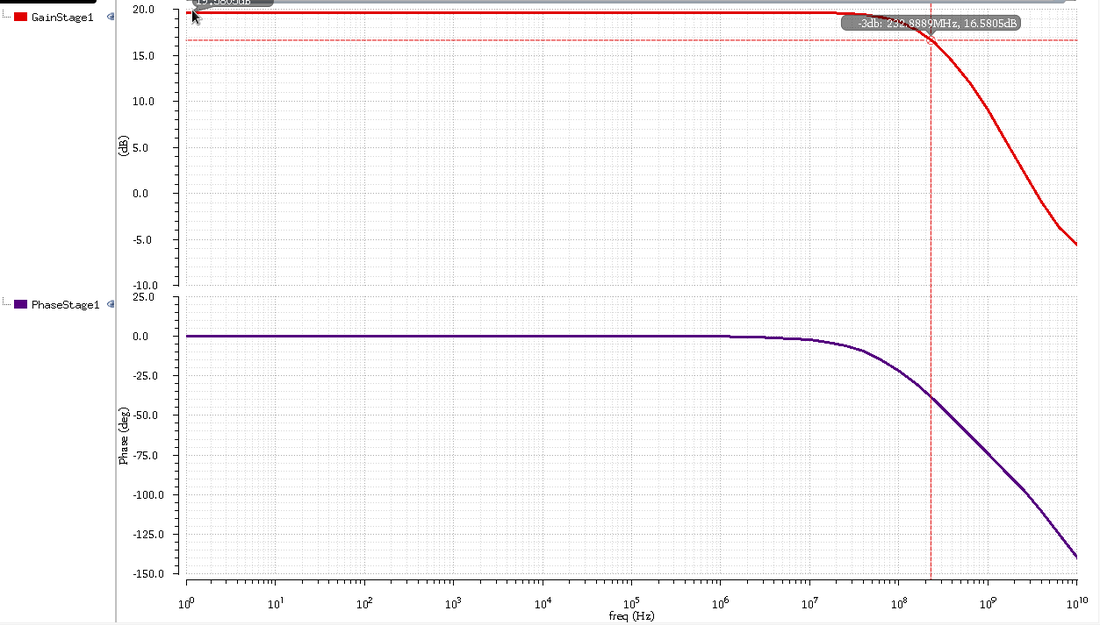

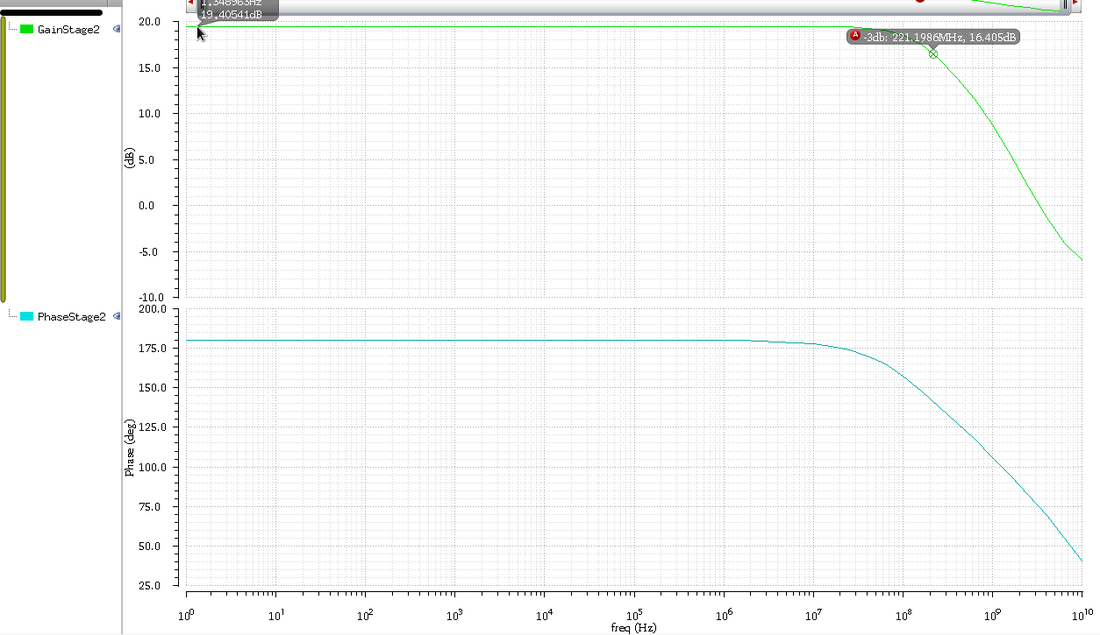

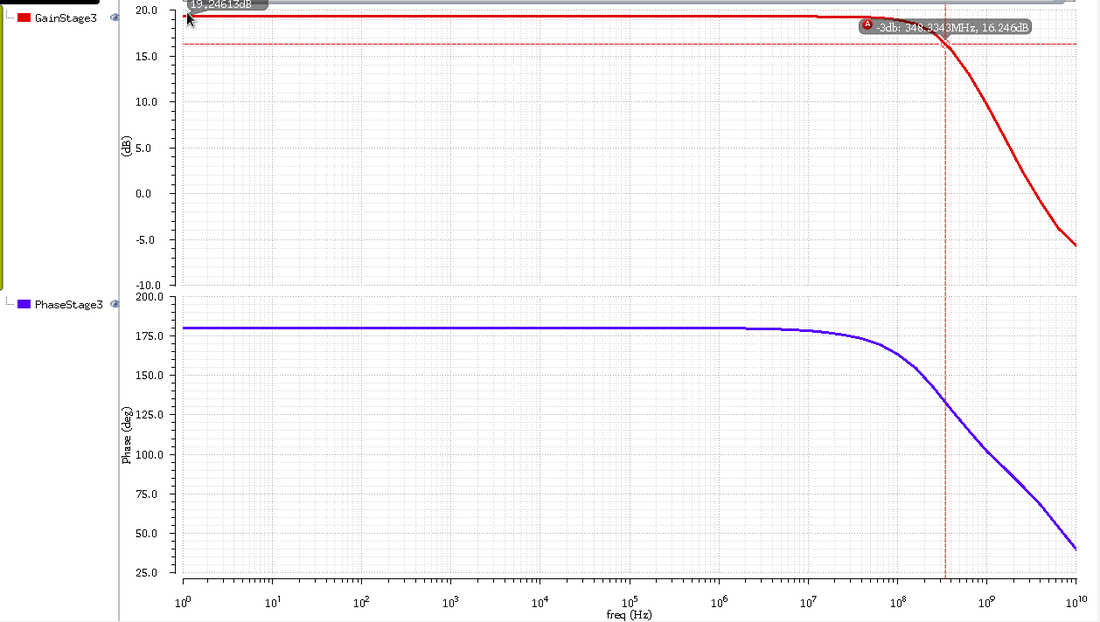

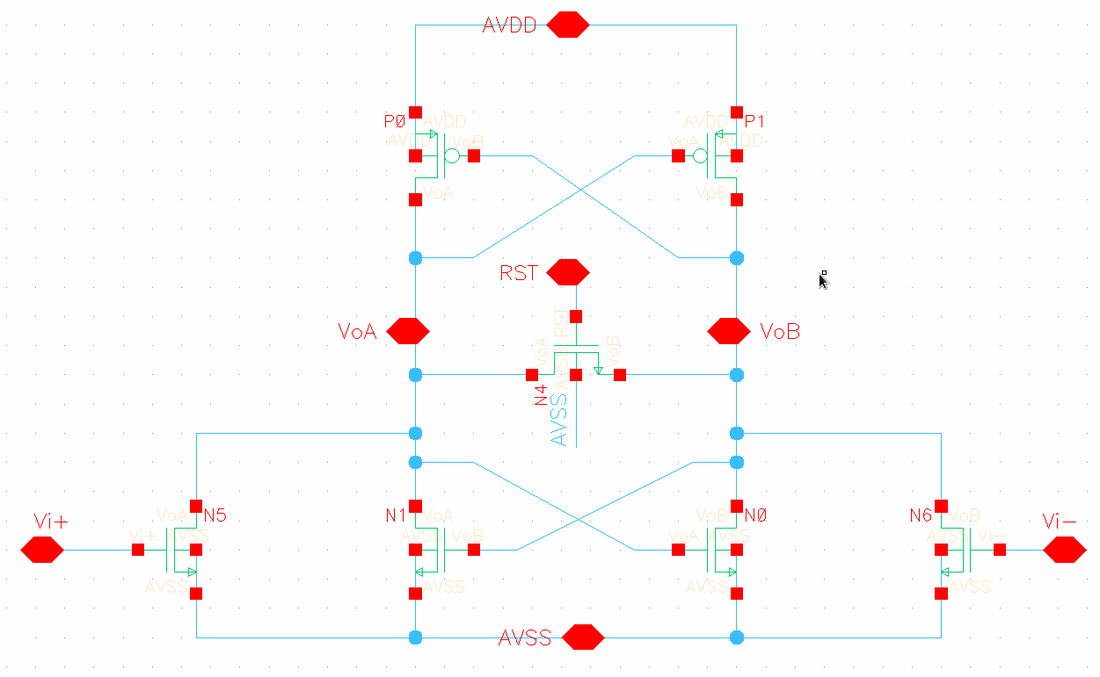

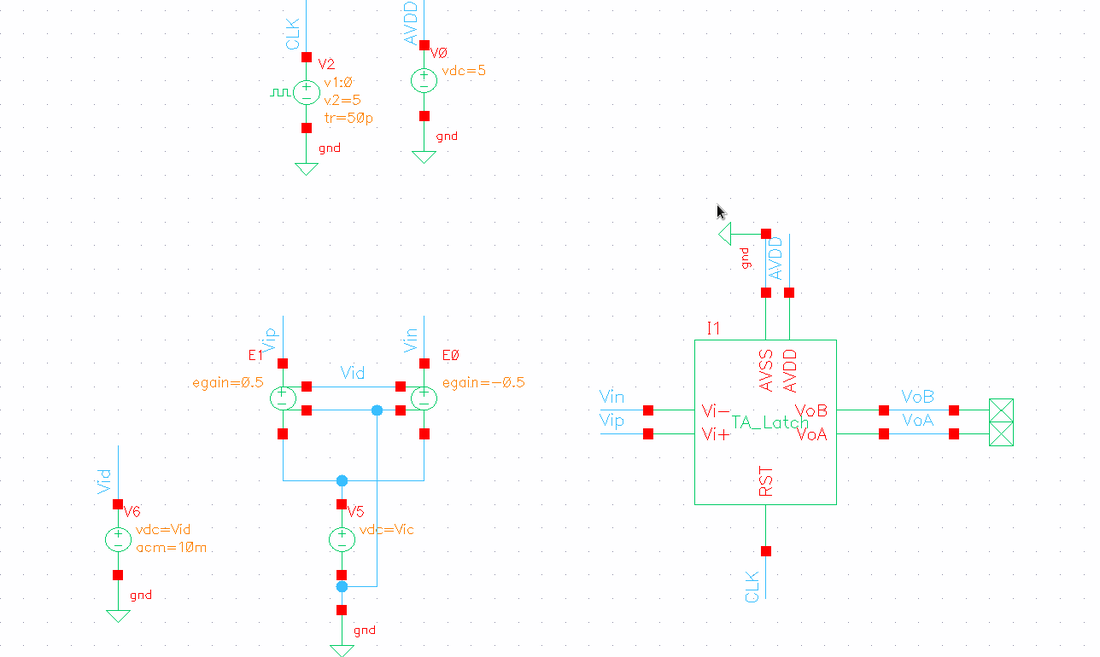

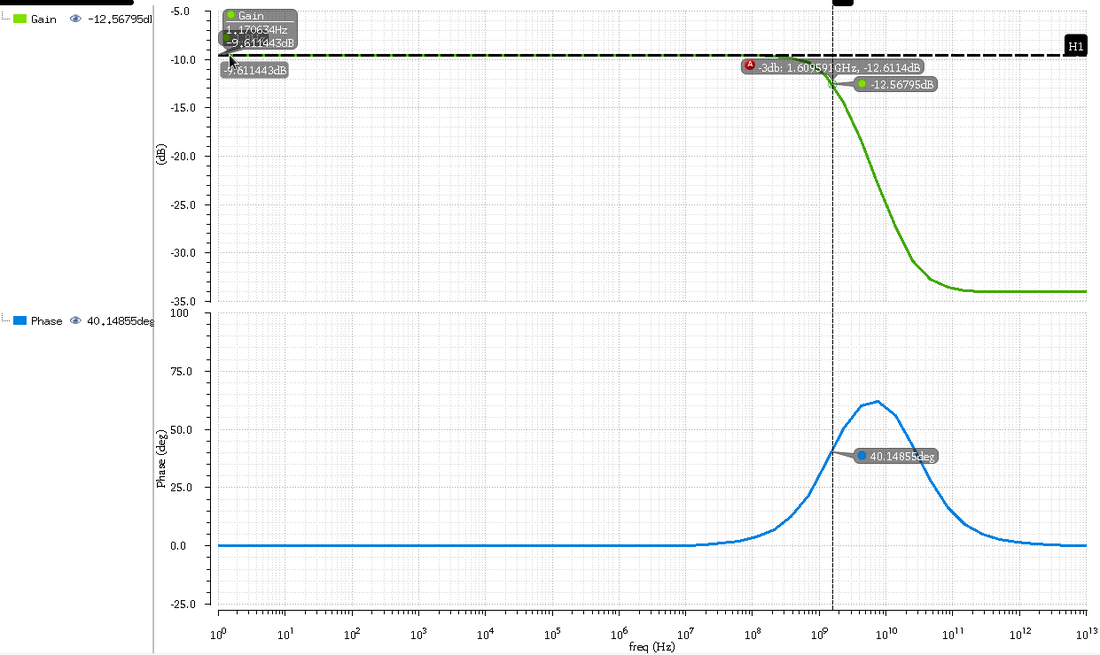

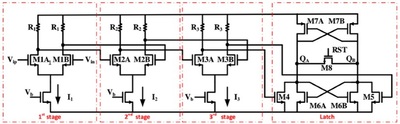

The comparator design consisted of four different stages. The first three are pre-amplifiers to amplify the difference in the two input signals. The last stage is a latch with a hysteresis loop to prevent switching from noise and to only change on a clock edge.

To create a comparator that will compare two voltages, we needed to amplify the input differential voltage to make it a binary signal. The quality of the signal does not matter as much as an operational amplifier because the signal is meant to clip to the positive and negative rails.

Pre-Amp(s)

Latch

The latch with a hysteresis loop is a sub-component of the comparator. In order to switch the comparator only on a positive clock edge, we use a latch.

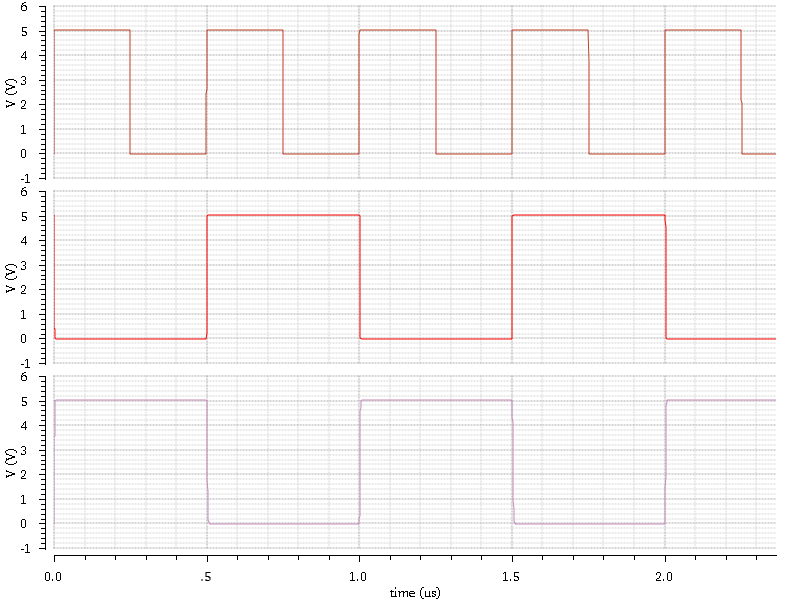

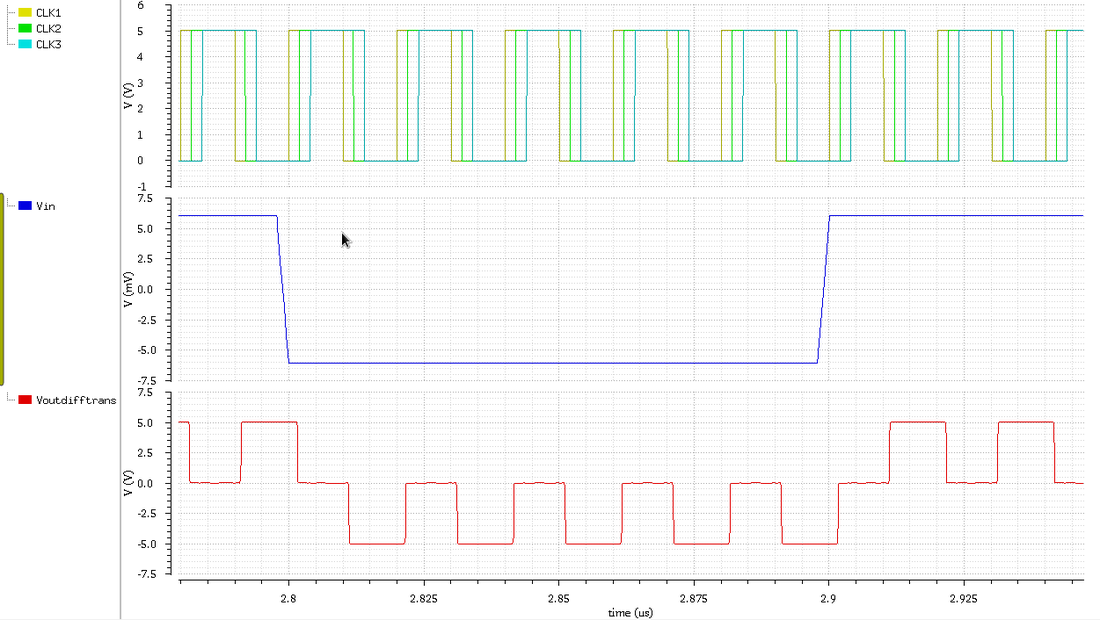

Overall Comparator Test

Below are the tests for the overall comparator. As we can see, the comparator operates as desired.

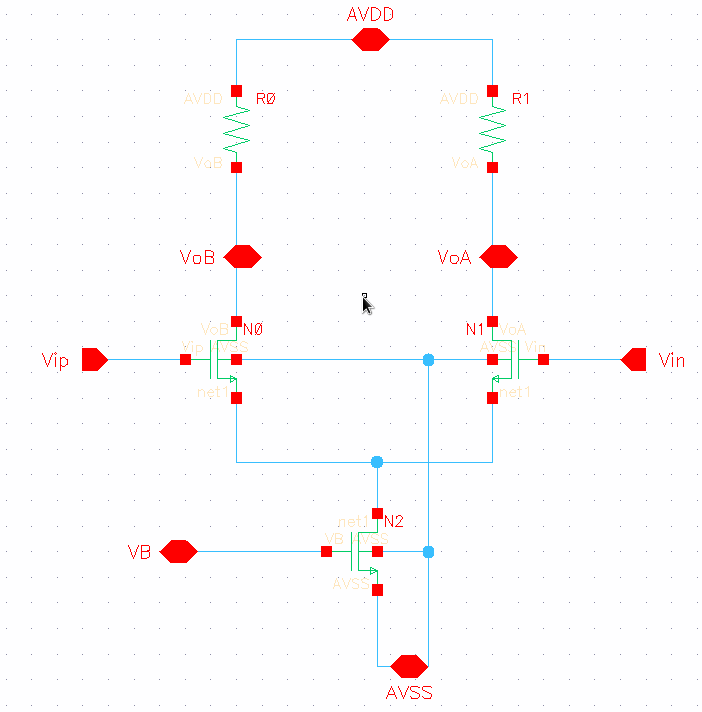

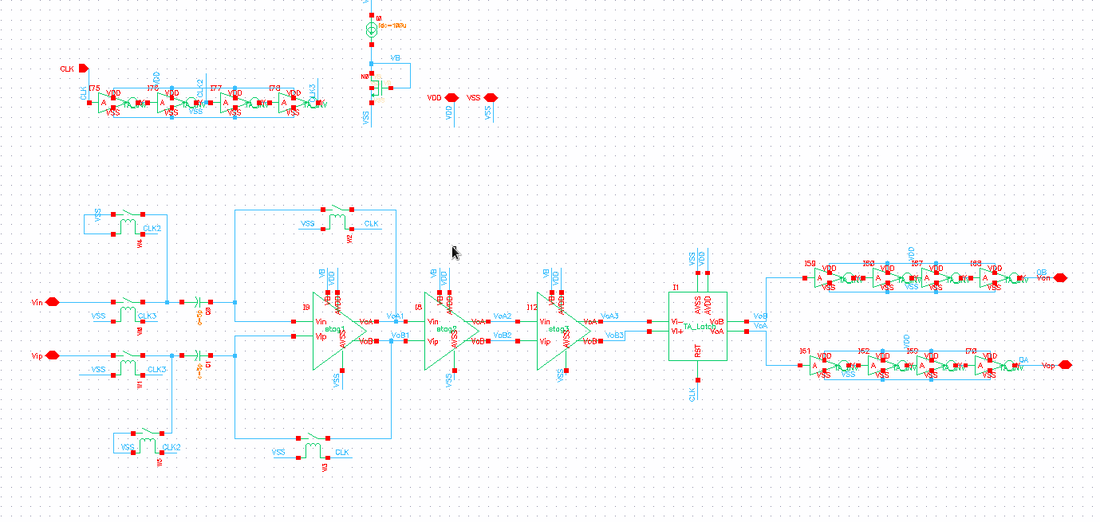

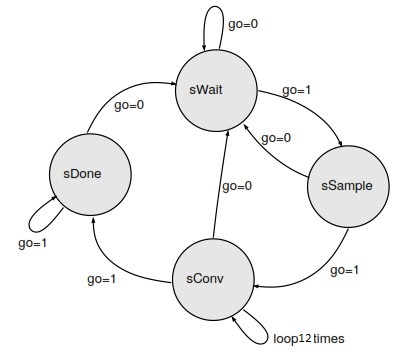

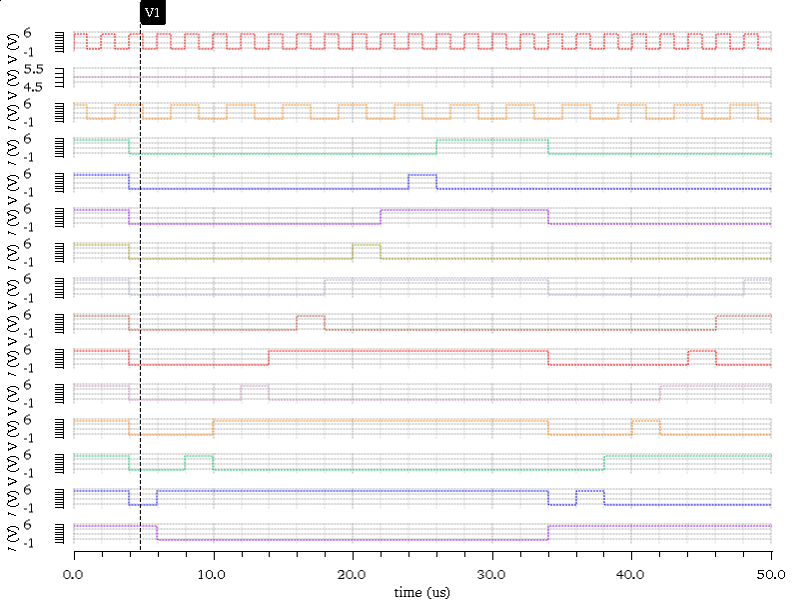

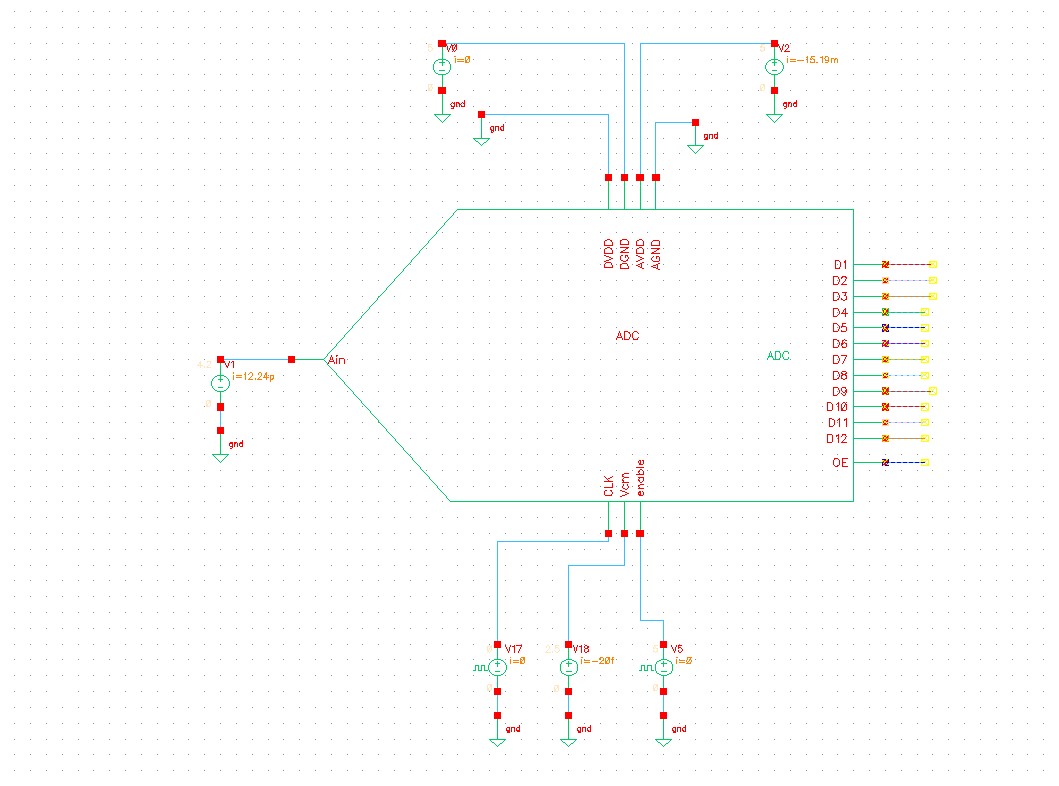

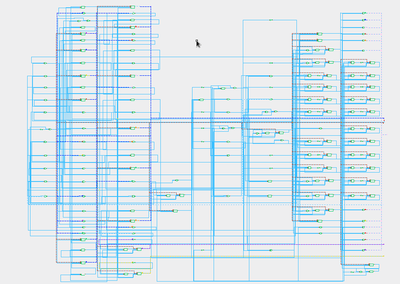

Successive Approximation Register Logic

|

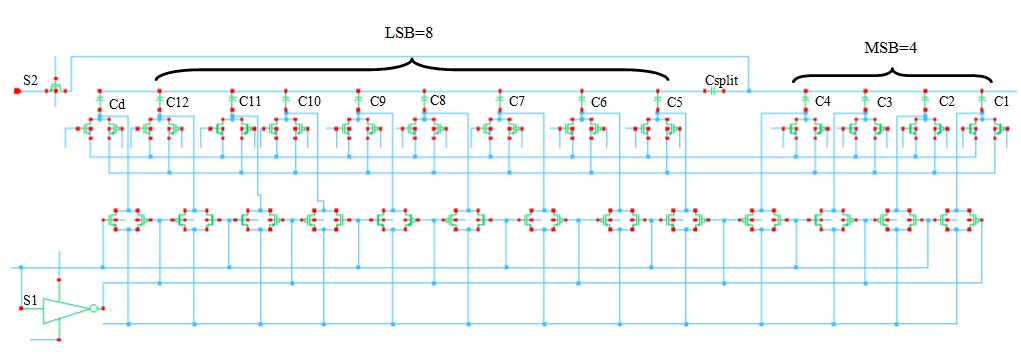

The controller repeats the process of changing the switch value starting with the most significant bit and going to the least significant bit to find the digital value to make the DAC output closest to Vin. This is the critical point where the efficiency and speed of the ADC is defined and where the DAC and comparator are put to use.

|

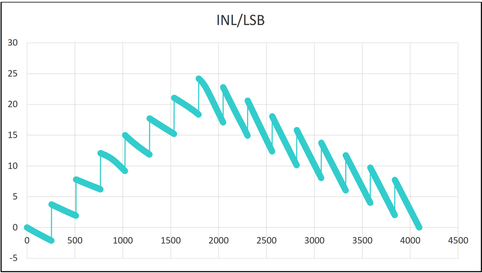

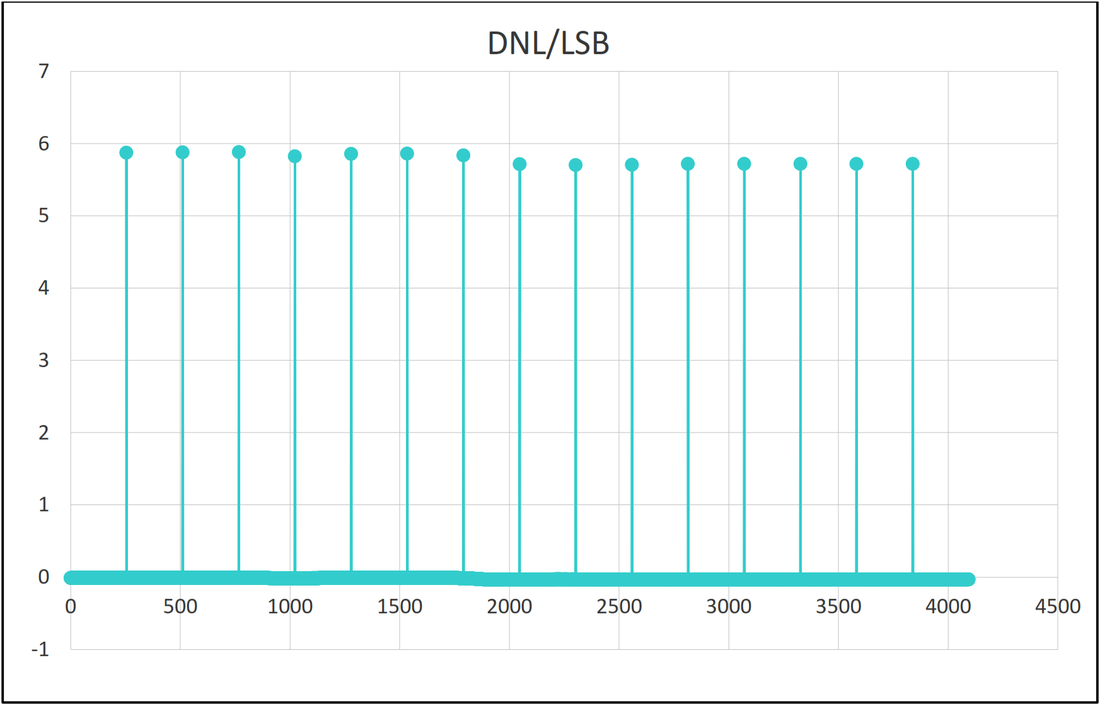

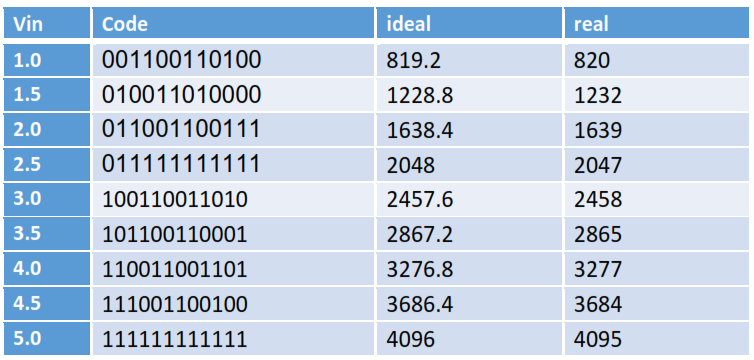

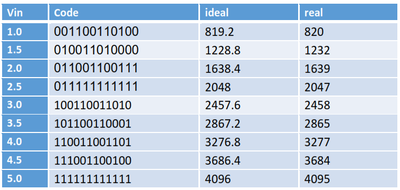

Overall ADC Results

Gallery

Lab Documents

| ee435finalprojectreport.pdf | |

| File Size: | 2078 kb |

| File Type: | |